# UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁ PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA E INFORMÁTICA INDUSTRIAL

HUDSON JORGE

# EXTENSIONS TO CLOUDSIM SIMULATOR BASED ON A FIRST ORDER PARASITIC COUPLING OVERHEAD MODEL TO STUDY THE CPU SCALATION IN CLOUDS SYSTEMS

DISSERTAÇÃO

CURITIBA

2018

# HUDSON JORGE

# EXTENSIONS TO CLOUDSIM SIMULATOR BASED ON A FIRST ORDER PARASITIC COUPLING OVERHEAD MODEL TO STUDY THE CPU SCALATION IN CLOUDS SYSTEMS

Dissertação apresentada ao Programa de Pósgraduação em Engenharia Elétrica e Informática Industrial da Universidade Tecnológica Federal do Paraná como requisito parcial para obtenção do grau de "Mestre em Ciências" – Área de Concentração: Informática Industrial.

Orientador: Emilio C. G. Wille

CURITIBA

Dados Internacionais de Catalogação na Publicação

Jorge, Hudson

Extensions to cloudsim simulator based on a first order parasitic coupling overhead model to study the CPU scalation in clouds systems [recurso eletrônico] / Hudson Jorge.-- 2019.

1 arquivo eletrônico (74 f.): PDF; 1,49 MB.

Modo de acesso: World Wide Web

Título extraído da tela de título (visualizado em 22 abr. 2019) Texto em inglês com resumo em português

Dissertação (Mestrado) - Universidade Tecnológica Federal do Paraná. Programa de Pós-graduação em Engenharia Elétrica e Informática Industrial, Curitiba, 2018

Bibliografia: f. 72-74.

1. Engenharia elétrica - Dissertações. 2. Processamento paralelo (Computadores). 3. Processamento paralelo (Computadores) - Simulação por computador. 4. Computadores - Redes. 5. Modelagem de sistemas complexos. 6. Dispositivos de treinamento simulado. I. Wille, Emílio Carlos Gomes. II. Universidade Tecnológica Federal do Paraná. Programa de Pós-graduação em Engenharia Elétrica e Informática Industrial. III. Título.

CDD: Ed. 23 – 621.3

Ministério da Educação Universidade Tecnológica Federal do Paraná Diretoria de Pesquisa e Pós-Graduação

# TERMO DE APROVAÇÃO DE DISSERTAÇÃO Nº 810

A Dissertação de Mestrado intitulada "*Extension to Cloudism Simulator Based on a First Order Parasitic Coupling Overhead Model to Study the CPU Scalation in Cloud Systems*" defendida em sessão pública pelo(a) candidato(a) **Hudson Jorge**, no dia 22 de outubro de 2018, foi julgada para a obtenção do título de Mestre em Ciências, área de concentração Telecomunicações e Redes, e aprovada em sua forma final, pelo Programa de Pós-Graduação em Engenharia Elétrica e Informática Industrial.

BANCA EXAMINADORA:

Prof(a). Dr(a). Emilio Carlos Gomes Wille - Presidente – (UTFPR) Prof(a). Dr(a). Luis Carlos Erpen de Bona - (UFPR) Prof(a). Dr(a). Elias Procópio Duarte - (UFPR)

A via original deste documento encontra-se arquivada na Secretaria do Programa, contendo a assinatura da Coordenação após a entrega da versão corrigida do trabalho.

Curitiba, 22 de outubro de 2018.

To my parents, that gave all they had, material and spiritual, to support my ambitions and achievements. My efforts are to honor them enough, even knowing it is an impossible task.

To my daughter and son, for the opportunity to give them what my parents gave to me.

To my friends, for the good advices and the knowledge shared.

To my mentor, for the patience and professionalism.

#### AGRADECIMENTOS

There are always a set of people that without them it would be impossible to achieve our projects and ambitions. There is not enough words to thanks all of them for all they gave in terms of support, knowledge, advice or just acceptance. But some are crucial in the long run projects, and this work is one of them.

Special thanks for my mentor Prof. Dr. Emilio C. G. Wille, for the patience in listening hours of contradictory explanations, correcting me and always putting on focus the target. Special thanks for my family, that supported long periods of absent, even when I was with them. I wish to thanks my business coleagues that helped me when I needed knowledge they have and shared gracefully.

In memory of Munir Jorge, my beloved Father.

#### **RESUMO**

JORGE, Hudson. EXTENSIONS TO CLOUDSIM SIMULATOR BASED ON A FIRST ORDER PARASITIC COUPLING OVERHEAD MODEL TO STUDY THE CPU SCALATION IN CLOUDS SYSTEMS. 74 f. Dissertação – Programa de Pós-graduação em Engenharia Elétrica e Informática Industrial, Universidade Tecnológica Federal do Paraná. Curitiba, 2018.

O aumento de performance em CPUs paralelas é dependente de muitos fatores como comportamento das aplicações, cache disponível, eficiência do uso do cache. Simuladores em computadores são usados para prever ou comparar a performance de processadores multi-core; eles são categorizados como modelos ciclo-precisos ou de alto nível. Os modelos cliclo-precisos são baseados na teoria de filas para passo-a-passo conduzir a simulação a executar as operações necessárias para consumir um modelo que representa o tamanho da aplicação. Os modelos de alto nível são usados para coletar, usualmente através de hardware adicional, informações não acessíveis que representam o comportamento do sistema em operação. Nos dois casos, eles são complexos porque uma longa sequência de filas (ciclo-preciso) controlam o processo, fazendo com que a simulação sejam muito demoradas. No caso de alto nível, muitas vezes é necessário um hardware completamente diferente do sistema real a fim de ler os estados necessários. Além disso, às vezes sistemas com lógica programável são usados para implementar o controle de cache, filas e protocolos de comunicação o que aumenta o tempo de execução, por causa as restrições de clock desse hardware adicional. Baseado em um modelo simples proposto por Kandalintsev e Lo Cigno, o Modelo BFO (First Order Performance), toda a complexidade da arquitetura interna é estudada como interferência parasítica de uma CPU/core lutando por recursos comuns. Eles introduziram um fator de acoplamento, que incorpora a essencia do comportamento de performance observado em um sistema. Neste trabalho, usamos o modelo BFO para implementar um simulador ciclo-preciso rápido capaz de manusear grandes sistemas. Para tanto o simulador CloudSim foi extendido para se comportar como um simulador ciclopreciso. Basicamente implementamos modelos de CPU e modelos de aplicação que poder dar conta da complexidade de diferentes tipos de cenários (comportamento de CPU distintos quando rodando diferentes tipos de aplicação). Usando medidas off line nós treinamos o modelo para extrair os fatores de acoplamento necessários para alimentar o simulador. Testamos o comportamento em pares para estar seguros de que a implementação poderia reproduzir os testes medidos. Nossas simulações consideram até 14 cores (no caso de m Xeon E5-2880v4) e para melhorar a qualidade dos resultados introduzimos um fator de correção para minimizar o erro observado (que parece ser exponencial), com bons resultados.

**Palavras-chave:** processamento paralelo, arquiteturas multi-core, computação de alta performance, technologia, simulação, modelamento de performance.

### ABSTRACT

JORGE, Hudson. EXTENSION TO CLOUDSIM SIMULATOR BASED ON A FIRST ORDER PARASITIC COUPLING OVERHEAD MODEL TO STUDY THE CPU SCALATION IN CLOUDS SYSTEMS. 74 f. Dissertação – Programa de Pós-graduação em Engenharia Elétrica e Informática Industrial, Universidade Tecnológica Federal do Paraná. Curitiba, 2018.

Parallel CPU performance scaling is dependent of many factors such applications behavior, cache available, efficiency of cache use. Computer simulators are used to predict or benchmark the performance of multi-core processors; they are categorized as cycle accurate or high-level models. The cycle accurate models are based on queue theory to step-by-step conduct the simulation to perform the operations needed to consume a model that represents the application size. The high-level models are used to collect, usually via additional hardware, not accessible information that represents the behavior of the running system. In those two cases, they are complex because a very long sequence of queues (cycle accurate) controls the process, making the simulation very time consuming. And in the case of high-level, sometimes it needs a complete different hardware from the actual system to read the needed states. In addition, sometimes programmable logic systems are used to implement the cache controls, queues and communication protocols what enlarges the running time, to accommodate the clock restrictions of the additional hardware. Based on a simple model proposed by Kandalintsev and Lo Cigno, the Behavioral First Order Performance Model (BFO), all the complexity of the internals of the architecture is studied as parasitic interference of one CPU/core fighting for shared resources. They introduced a coupling factor, which incorporates the essence of the observed performance behavior in a system. In this work, we used the BFO model to implement a fast cycleaccurate simulator capable of handling even large systems. To do it the CloudSim simulator was extended to behave as a cycle-accurate simulator. Basically we implemented CPU and application models that can handle the complexity of the different types of scenarios (distinct CPU behavior when running different kinds of applications). Using off line measurements we trained the model to extract the coupling factor needed to feed the simulator. We tested the pairwise behavior to make sure that the implementation could reproduce the measured tests. Our simulations consider up to 14 cores (in case of Xeon E5-2880v4) and to improve the results quality we introduced a correction factor to minimize the (seemly exponential) error observed, with good results.

**Keywords:** parallel processing, multi-core architectures, high performance computing, technology, simulation, performance modeling.

# LISTA DE FIGURAS

| FIGURA 1 -  | Speedup vs. Number of CPUs                                                  | 22 |

|-------------|-----------------------------------------------------------------------------|----|

| FIGURA 2 -  | Speedup vs. serial fraction <i>s</i>                                        | 23 |

| FIGURA 3 -  | Scalability of Fixed-Size (Amdahl's law) and Fixed-Time Models              |    |

|             | (Gustafson's law).                                                          | 26 |

| FIGURA 4 -  | Typical Memory Organization in Multi-core Systems                           | 30 |

| FIGURA 5 -  | RPM First-Level Cache (FLC) implementation.                                 | 34 |

| FIGURA 6 -  | RPM Second-Level Cache (SLC) implementation.                                | 34 |

| FIGURA 7 -  | Internal Organization of Core Model - Power4 single core modeled            | 35 |

| FIGURA 8 -  | Internal Organization of 4-Core System Model - Power4 CPU modeled           | 35 |

| FIGURA 9 -  | Task Load definition: Tasks schedule in one CPU core in one slice of time   |    |

|             | Τ                                                                           | 37 |

| FIGURA 10 - | Interference between tasks running on different cores. (a) Task A running   |    |

|             | on CPU core c1, with no interference of CPU core c2, (b) Task A running     |    |

|             | on CPU core c1 is interfered by task B running on CPU core c2.              | 38 |

| FIGURA 11 - | CloudSim Layered Design                                                     | 43 |

| FIGURA 12 - | CloudSim Layered Architecture.                                              | 44 |

| FIGURA 13 - | CloudSim Layered Architecture                                               | 46 |

|             |                                                                             | 48 |

|             |                                                                             | 49 |

| FIGURA 16-  | Extensions on Cloudlet class and object instantiation helped by             |    |

|             | CloudletCorrection class.                                                   | 50 |

| FIGURA 17-  | Extensions on <i>Cloudlet</i> class and object instantiation helped by      |    |

|             | CloudletCorrection class.                                                   | 51 |

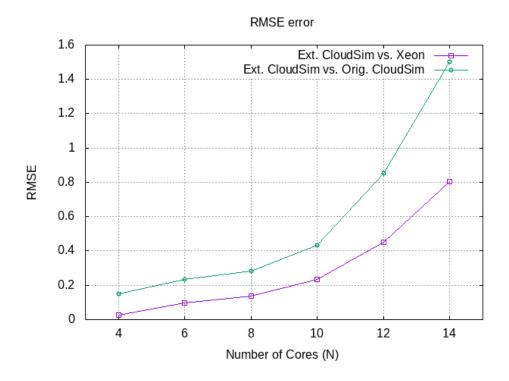

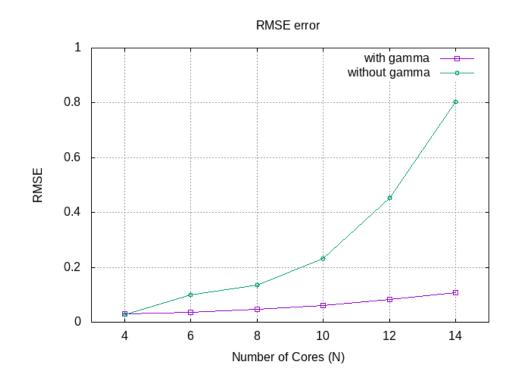

| FIGURA 18 - | RMSE error vs. Number of cores.                                             | 67 |

| FIGURA 19 - | RMSE error vs. Number of Cores. With $\gamma = 0.1$ shows good reduction in |    |

|             | RMSE error                                                                  | 68 |

# LISTA DE TABELAS

| TABELA 1 –  | Usage of taskset pinning flag. The flag is the hexadecimal interpretation when $OFF = 0$ and $ON = 1$ . | 55 |

|-------------|---------------------------------------------------------------------------------------------------------|----|

| TABELA 2 –  | Instructions per second (MIPS) calculated for each CPU type in the ideal                                | 59 |

|             |                                                                                                         |    |

|             | Coupling Factors $\beta_{A \to B}$ for OPTERON 2214HE                                                   |    |

|             | Coupling Factors $\beta_{A \to B}$ for XEON E5-2680v4                                                   | 60 |

|             | Coupling Factors $\beta_{A \to B}$ for i7-6500U                                                         | 60 |

| TABELA 6 –  | CloudSim simulating various stressors results with Opteron 2214HE                                       |    |

|             | parameters (declared in CloudSim with MIPS=3000)                                                        | 62 |

| TABELA 7 –  | CloudSim simulating various stressors results with Xeon E5-2680v4                                       |    |

|             | parameters (declared in CloudSim with MIPS=6000)                                                        | 63 |

| TABELA 8 –  | CloudSim simulating various stressors results with i7-6500U parameters                                  |    |

|             | (declared in CloudSim with MIPS=5000)                                                                   | 64 |

| TABELA 9 –  | RMSE between CloudSim simulations over stressors and real world                                         |    |

|             | measurements with Opteron 2214HE. Tests calibrated for 320s of runtime.                                 | 65 |

| TABELA 10-  | RMSE between CloudSim simulations over stressors and real world                                         |    |

|             | measurements with Xeon E5-2680v4. Tests calibrated for 320s of runtime.                                 | 65 |

| TABELA 11 – | RMSE between CloudSim simulations over stressors and real world                                         |    |

|             | measurements with i7-6500U. Tests calibrated for 320s of runtime                                        | 65 |

| TABELA 12-  | Testing the model accuracy calculating RMSE between Extended                                            | 00 |

|             | CloudSim simulations and real world XEON E5-2680v4. In addition the                                     |    |

|             | RMSE between Extended CloudSim and the Original CloudSim (that uses                                     |    |

|             | the linear CPU escalation model). Tests calibrated for 320s of runtime to                               |    |

|             |                                                                                                         | 66 |

|             | permit cache stabilization.                                                                             | 00 |

| TABELA 13-  |                                                                                                         |    |

|             | simulations and real world XEON E5-2680v4 and Extended CloudSim with                                    |    |

|             | Correction Factor $\gamma = 0.1$ . Tests calibrated for 320s of runtime to permit                       |    |

|             | cache stabilization.                                                                                    | 68 |

|             |                                                                                                         |    |

# LISTA DE SIGLAS

| HPC   | High Performance Computing                       |

|-------|--------------------------------------------------|

| BCE   | Base Core Equivalent                             |

| SLATE | System-Level Analysis Tool for Early Exploration |

| BCE   | Base Core Equivalent                             |

| FPGA  | Field Programmable Gate Array                    |

| API   | Application Programming Interface                |

| DVFS  | Dynamic Voltage and Frequency Scaling            |

| MIPS  | Million Instructions Per Second                  |

|       |                                                  |

| GPU   | Graphics Processing Unit                         |

| SSD   | Solid State Disk                                 |

|       |                                                  |

# SUMÁRIO

| 1 INTRODUCTION                                                                             | 13 |

|--------------------------------------------------------------------------------------------|----|

| 1.1 MOTIVATION                                                                             | 15 |

| 1.2 OBJECTIVES                                                                             | 17 |

| 1.2.1 General Objectives                                                                   | 17 |

| 1.2.2 Specific Objectives                                                                  | 17 |

| 1.3 STRUCTURE OF THE DISSERTATION                                                          | 18 |

| 2 PARALLEL PROCESSING PERFORMANCE MODELS                                                   | 20 |

| 2.1 PERFORMANCE IN MULTI-CORE PARALLEL SYSTEMS REVIEW                                      | 20 |

| 2.2 AMDAHL'S LAW, DEFINITIONS AND CONSEQUENCES                                             | 21 |

| 2.2.1 Amdahl's Law and speedup in multi-core systems                                       | 22 |

| 2.2.2 Amdahl's Law Corollary - The Fixed Size Law Applied to Multi-core                    | 23 |

| 2.3 TIME FIXED LAW, THE GUSTAFSON'S LAW                                                    | 25 |

| 2.4 MEMORY BOUND MODEL, THE SUN AND NI'S LAW                                               | 27 |

| 2.5 MEMORY WALL PROBLEM                                                                    | 29 |

| <b>3 PERFORMANCE MODELING</b>                                                              | 32 |

| 3.1 MODELING FOR PERFORMANCE PREDICTION                                                    | 32 |

| 3.1.1 RPM - High-Level Model                                                               | 32 |

| 3.1.2 SLATE - Cycle-Accurate Model                                                         | 34 |

| 3.1.3 The Behavioral First Order (BFO) CPU Performance Model                               | 36 |

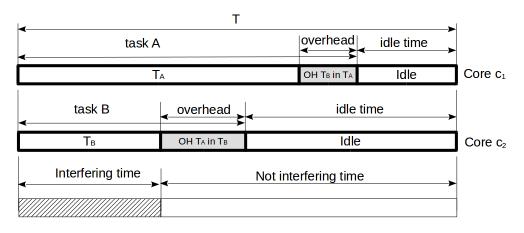

| 4 EXTENSIONS ON CLOUDSIM TO IMPLEMENT THE BFO MODEL                                        | 42 |

| 4.1 THE CLOUDSIM                                                                           | 42 |

| 4.1.1 CloudSim Design                                                                      | 42 |

| 4.1.2 CloudSim Architecture                                                                | 44 |

| 4.1.3 CloudSim Classes                                                                     | 45 |

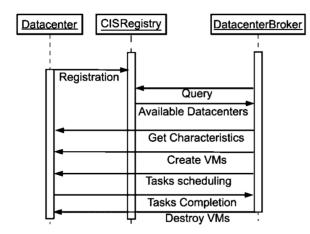

| 4.1.4 Datacenter Internal Processing                                                       | 48 |

| 4.2 FIRST ORDER BEHAVIORAL MODEL IMPLEMENTATION IN CLOUDSIM                                | 49 |

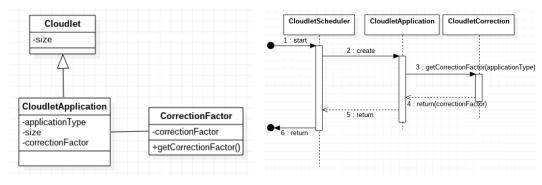

| 4.2.1 Cloudlet Class Extension                                                             | 49 |

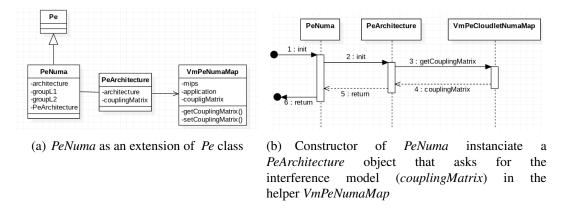

| 4.2.2 <i>Pe</i> Class Extension                                                            | 50 |

| 4.2.3 PowerHost Classes Overwriting                                                        | 51 |

| 4.2.4 Datacenter modeled by XML file                                                       | 51 |

| <b>5</b> FRAMEWORK FOR MULTI-CORE SYSTEMS EVALUATION                                       | 53 |

| 5.1 OVERHEAD MEASUREMENTS                                                                  | 53 |

| 5.1.1 How to empirically obtain the coupling factors $\beta$                               | 55 |

| 5.1.2 Testing Programs and Hardware configurations                                         | 57 |

| 5.1.3 Training Phase: Results of the calibration tests                                     | 58 |

| 5.1.4 Simulation Phase: Validation of extensions made on CloudSim                          | 60 |

| 5.1.4.1 Part I: Reproducing the ideal scenarios                                            | 61 |

| 5.1.4.2 Part II- Interference in Pairwise Scenarios                                        | 61 |

| 5.1.5 Generalization Phase - Use of Extended CloudSim to predict the behavior of different |    |

| loads scenario                                                                             | 64 |

| 5.1.6 Refining the model to improve results with increased number of cores                 | 66 |

| 6   | CONCLUSIONS AND FUTURE RESEARCH                    | 69 |

|-----|----------------------------------------------------|----|

| 6.1 | CONCLUSIONS OF THE MODEL BEHAVIOR AND THE CLOUDSIM |    |

|     | EXTENSIONS IMPLEMENTATION                          | 69 |

| 6.2 | LESSONS LEARNED AND FUTURE WORK                    | 71 |

| RE  | FERENCES                                           | 72 |

#### **1** INTRODUCTION

One well known empiric result in HPC (High Performance Computing) area is that *n* identical CPUs working in parallel will not deliver *n* times the speed of one CPU alone, independent of the architecture used for interconnect them. There are many reasons for that, for example memory and cache availability, I/O interruptions and disk wait time. This measurable behavior points towards that no multi-CPUs architecture can give exclusive resources to each individual CPU, making the overall performance decreases, due to the shared resources competition among the CPUs. In addition to it, the software also play an important role since it should be designed to make use of this parallel CPUs environment, implementing algorithms optimized for this parallel architecture.

This has been a long time discussion, that probably started with the famous observation of Amdahl (AMDAHL, 1967) that statistically a software execution in a multi-CPU environment can be divided in two parts, the parallel ratio that represents the fraction of the execution time where the CPUs have all the resources (physical and logical) available to execute their jobs and the serial ratio that represents the fraction of the execution time where the CPUs have be free or available. In the time of Amdahl's observation the serial fraction was estimated to be as big as 30%.

Overtime, new architectures came to better supply the CPUs with promptly available resources, it was pushed by the needs of the supercomputation area, these new architectures along with optimized software algorithms pushed the HPC area to new standards. Gustafson (GUSTAFSON, 1988) noticed that the Amdahl's law was not predicting well the measured performance in his lab. The key assumption he stated is that Amdahl's law was too restrictive because assumed that the serial fraction remained the same size independent of the problem size to be computationally solved, that is why nowadays the Amdahl's law is also known as *Fixed Size* law. According to Gustafson, the software designers make use of the new multi-CPU architecture resources and developed new algorithms that escalates down the serial fraction in

the same proportion of the problem size. This means that if the problem is doubled in size, the serial fraction is halved. This is known as Gustafson's law or *Fixed Time* law. It is *Fixed Time* because the serial fraction has the same absolute time independent of the problem size.

This discussion, was pacified for some time in HPC area, because the *Fixed Time* law assured that the multi-CPU architectures could perform very well if the software (Operational System (OS) and Algorithms) was designed to extract the best of these architectures. However, in the domestic and general purpose computation area the single CPU architecture was the common approach, since the Moore's law (MOORE, 1965) was still delivering results. In the servers market, very limited multi-core CPUs architectures were available for use, mainly because of the costs to implement these chips. Sudenly it all changed, mainly because of the Moore's law failings (TRACK et al., 2017), the multi-core approach presented as the only viable solution to continue the exponential growth of the power computing.

Since than, the discussion of CPU performance scaling reopenned, the main driver is because, even if the multi-core CPUs implementations are based on HPC architectures, they are more limited in a silicon chip because of restricted available space and limitations of the interconnection topologies possible to be implemented between the processors. For example some supercomputers implement hypercubic interconexion topology, what is hard to implement in silicon. Based on these limitations Marty and Hill (HILL; MARTY, 2008) have developed a corolary of the Ahmdahl's law, based on the concept of BCE (Base Core Equivalent). This work served as a baseline for Sun and Ni's work (SUN; NI, 1990), they created a model adherent to multi-core processor architectures, showing that they can perform near to Gustafson's law if there is enough cache memory available inside the chip. Moreover, Sun and Chen (SUN; CHEN, 2010) showed that it is possible to perform reasonably well even in presence of the *Memory Wall* problem (that is the disparity between how fast a CPU can operate on data and how fast it can get/put data on memory), but the effort is to be put in faster and larger cache memories and algorithms to clean it from leftover garbage.

The statistical models are fundamental to guide the research and industry on where to put efforts to improve performance over the generations of multi-core processors, as well as guide the software research to improve the use of the parallel architecture. However, they cannot predict the actual performance, also known as speed up, of a system based on the architecture and the software currently running on top of it. Therefore, there is room for other kind of performance models, one capable to predict the performance in the systems based on observable statistics collected on runtime. There are several works in this area, usually they are or too complex for implementation in real systems or are based on "hard to measure" parameters. For example, Barroso et. al. (BARROSO et al., 1995) created the RPM (Rapid Prototyping for Multiprocessor) an engine based on queue analysis, it presents a very good precision on the predictions, but it is slow to run since it executes the pipe of instructions in dedicated hardware (like cache and cache controller) to access the needed cache statistics. Nanda et. al. (NANDA et al., 2000) developed MemorIES that substitute physically the L1, L2 and L3 caches by a dedicated hardware capable to collect the cache statistics and calculate the processor's performance. This model is used to orient the design of servers and besides being faster then other models it uses parameters inaccessible in commercial servers.

To address the need for a model capable of deliver good and fast results based on observable statistics (in multi-core processors, usually the HPC counters) Kandalintsev and Lo Cigno (LO CIGNO; KANDALINTSEV, 2012) proposed a simple model based on the measured behavior an application presents when running on the multi-core system in controlled conditions and corrects it for the normal conditions of use. This model is further developed in Kandalintsev PhD thesis (KANDALINTSEV, 2016) "*Application Interference in Multi-Core Architectures: Analysis and Effects*" where a methodology to collect the parameters of the model are described as well as the methodology to test the model against the real world systems, even a methodology to collect the statistics to feed online algorithms, specially in case of CRM (Cloud Resource Manager) implemented to use the model to improve the decision of resource allocation. This work is one of the pillars of our work, and will be extensively explained in further chapters.

#### 1.1 MOTIVATION

In the literature, performance estimation tools for computing systems are mainly of two category: high-level models and precise cycle accurate simulators (KUNKEL et al., 2000). The second category give almost exact results, one example of it was implemented by Bergamaschi et. al. (BERGAMASCHI et al., 2007), resulting in a tool named SLATE (System-Level Analysis Tool for Early Exploration). This tool presented nearly exact results, but it is very time consuming, being helpful to orient computing systems design for example, since it can predict the actual task performance and point out bottlenecks. This result in a tool not suited to quick decisions that a live running system sometimes have to do, for example scheduling of tasks or thread switching.

On the other hand, the high-level models do not touch the behavior of the processors. These models are based on empirical observations of the overall system performance, or are based on abstract models (that can be split in several loosely coupled models). One example of this approach was proposed by Torrelas et. al. (TORRELLAS et al., 1990), where a queueing network model of the memory architecture of multi-CPU systems showed good results for some class of tasks. One problem with this approach is that some parameters in the model are not directly measured, but rather are estimated. Other problem is that the actual CPU role is not take into acount, making the model not suitable to simulating programs purposes. Refinements on the model were done resulting in SPLASH (Stanford Parallel Applications for Shared-memory) (SINGH et al., 1992) that is a set of parallel applications for use in the design and evaluation of shared-memory multiprocessing systems.

In our point of view, a new alternative to approach the CPU performance model is the work by Kandalintsev named "A behavioral first order CPU performance model for clouds management" (LO CIGNO; KANDALINTSEV, 2012). This simple model proposes a CPU centric model, based only on measurable parameters, capable to produce better approximations of the real systems performance than the actual linear CPU scaling performance paradigm usually present in the literature (JIANG et al., 2012), (SHRIVASTAVA et al., 2011), (TANG et al., 2007) and (FELDMAN et al., 2009). The model avoids to touch CPU internals, what makes it computationally very fast and suitable to be implemented in simulators, since it is possible to model the CPU performance individually.

The idea of being possible to simulate the CPU performance when running different tasks is one key driver in the present work. The idea is that if we modify an existing simulator to implement the Kandalintsev's model, it could enhance the results giving a better simulator platform to researchers and developers to implement their own algorithms (like schedulers, load balancers, and so on). Reviewing the literature, we choose CloudSim simulator (CALHEIROS et al., 2011), because it is flexible enough to be extended, it is free software, well documented and most of all (besides being created to Cloud Simulations purpose) it could be adapted to simulate what we were interested, that is the CPU scaling performance in multi-core computational systems.

#### 1.2 OBJECTIVES

#### 1.2.1 GENERAL OBJECTIVES

The main objective of this work is to extend the CloudSim Simulator, implementing into it the BFO (Behavorial First Order) performance model of Kandalintsev and Lo Cigno. This objective is divided in two sub-objectives, the first is to improve the accuracy of the results presented by the original CloudSim in terms of the actual performance of real multi-core systems. The second objective corresponds to propose an extended model to explicitly consider te number of cores that work in parallel. The original BFO model presents an elevated level of error , specially when the number of parallel cores are higher than 8 cores. Our extended model can improve the simulations results from CloudSim.

CloudSim is a good choice because it follows a common paradigm, that the CPU performance scaling is linear, that is reasonable considering that it is very common that the systems, specially in Clouds that are the focus of CloudSim, are consuming little computation power compared with what the system has available. This will be used in favor of this research, because we have granted a simulator that has no performance correction implemented, and we guarantee that our implementation is unique for this purpose.

The BFO model proved to be a good choice, because it can give us the baseline to compare the real performance of multi-core systems against the simulator (calibrating it), and then use it to validate the implemented model when the number of cores raise or the size of the problem increases or decreases. It is expected that the result of these cycle (implementation of the model, training of the simulator, generalization of use cases in the simulator, comparison with real systems measurements) will lead us to an implementation adherent with real world scenarios, as well as with a method to serve anyone interested in implement its own research in this area.

#### 1.2.2 SPECIFIC OBJECTIVES

The specific objectives of this work are:

1. To validate the BFO model by comparing it against results from an experimental system. This is important to gain experience on the performance counters available in the processors, as well as the correct use of the tool to generate the load for the CPUs: the stressors *stress-ng* (UBUNTU-WIKI, 2008), and the tool to read the counters *perf* (WIKI, 2015).

- 2. To implement the BFO model in the CloudSim simulator. This is made via extension of some classes and creation of brand new classes inside the CloudSim package.

- 3. To validate the extended CloudSim against the real world systems data collected.

- 4. To use the extended CloudSim to predict the behavior of different loads patterns.

- 5. To propose and test an extended model that considers explicitly the number of cores that work in parallel.

## 1.3 STRUCTURE OF THE DISSERTATION

This dissertation has six chapters (Introduction, Parallel Processing Performance Models, Performance Modeling, Extensions on CloudSim to Implement the BFO Model, Framework for Multi-Core Systems Evaluation, Conclusions and Future Research).

In the chapter *Parallel Processing Performance Models*, we describe in detail some important models to characterize the CPU escalation problem, that is the Amdahl's law (or Fixed Size law), the Gustafson's law (or Fixed Time law) and the Sun and Ni's law (or Memory Bound law). These are statistical models constructed to speculate about the scaling capabilities of a parallel computational system, and the multi-core processors are such a system.

In the chapter *Performance Modeling* starts with a bibliographic review where the cycle accurate and high-level models are explained and one of a kind in described, the RPM (a high-level model) and the SLATE (a cycle-accurate model). In the sequence, the model created by Kandalintsev and Lo Cigno is explained in details, as well as it is described how to obtain the coupling factor  $\beta$  using off line procedures.

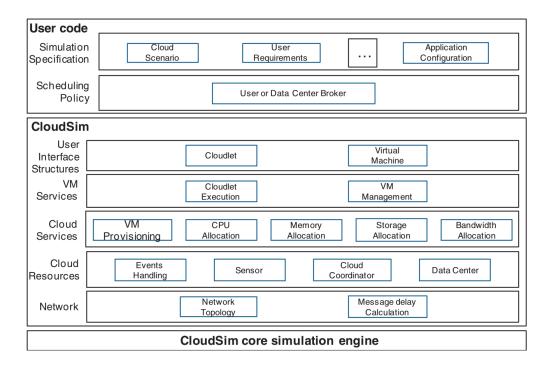

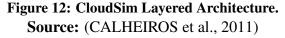

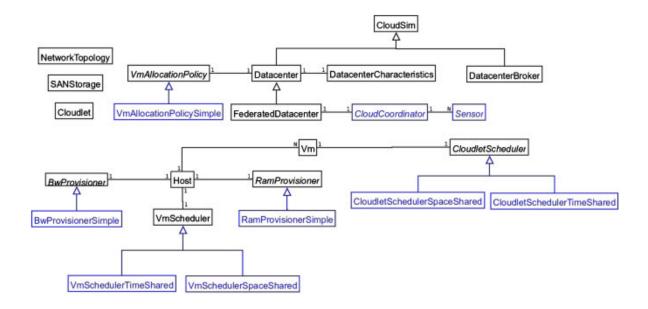

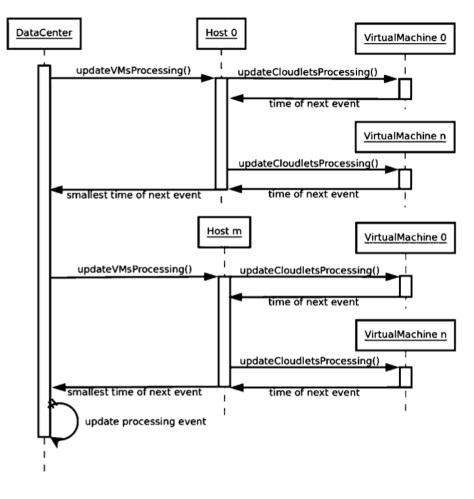

In the chapter *Extensions on CloudSim to Implement the BFO Model* we see the actual implementation of the BFO model in CloudSim. It is shown the UML diagrams with the detailed implementation of the model. The first part shows the CloudSim core simulation engine, and the second part is dedicated to the implementation.

The chapter *Framework for Multi-Core Systems Evaluation* is dedicated to explain the methodology followed to train and to test the model using measurements done in real world systems. It is done as a comprehensive guide on how the tests and corrections were made to train the simulator and the use of it to extend the results, comparing it with the real world computational systems. In addition, at the end we propose an extension of BFO model based in a logarithmic rule to correct the coupling factor as a function of the number of parallel cores active. This reduces the RMSE error that grows with the number of cores.

In the chapter *Conclusions and Future Research* are compiled all the findings, as well as, the observations and the insights the research leaded us.

## 2 PARALLEL PROCESSING PERFORMANCE MODELS

## 2.1 PERFORMANCE IN MULTI-CORE PARALLEL SYSTEMS REVIEW

By empirical measurements we know that when working with multi-core CPUs the overall performance (speed up) does not grow linearly with respect to the number of available cores. This is related to use of shared resources during runtime, for example, internal caches, bus, interfaces, I/O, RAM, and network. Because of it, the cores cannot run independently making the combined performance (speed up) be less than the number of number of cores working in parallel.

This problem was first addressed by Amdahl (AMDAHL, 1967) and leaded to a discouragement of manufacturers in the earlier times of the computer industry. Some decades after that, Gustafson (GUSTAFSON, 1988) revisited the problem because the microarchitecture of modern computation had overcome some of the architectural problems saw by Amdahl, showing that for multi-CPU scenario the performance scaled less restrictively than Amdahl's assumptions, arguing that software designers adapt their algorithms to scale down the serial part in a way that the execution time is fixed. After some years Sun and Ni (SUN; NI, 1990) showed how memory plays an important role on the performance, assuming that the execution of an algorithm scales in the memory (specially caches), the model is known as memory bound. This model is promising and has influenced the foundations of modern multicore architectures in a sense to improve memory access avoiding what is known as memory wall problem. As one of the goals of the actual work is to predict the CPU scaling based on a behavioral model where the inputs are collected by data collected in an experimental system, a complete understanding of those three laws is of fundamental importance, since it gives us the ground to discuss the results and what can be improved.

#### 2.2 AMDAHL'S LAW, DEFINITIONS AND CONSEQUENCES

The first work that called attention to the scalability problem in parallel computer systems was done by Eugene Amdahl (AMDAHL, 1967), and consists of an observation that the execution time is formed by two parts, the one that benefits with the parallel processing, and the other that is irreducible and does not benefit with the parallel processing. He divided the processing timespan in two parts, the *parallel* that is related to the amount of time that the CPUs run independently, with no conflicts with the other CPUs, and can be expressed as the ratio p with  $p \in [0,1]$ . The second part is related to amount of time that cannot be reduced by the parallelism, due to the conflicts in the shared resources, this is called *serial* execution time and can be expressed as the ratio s with  $s \in [0,1]$  and s = 1 - p. Equation 1 shows the mathematical formulation of the Amdahl's law, where the *speedup* S(n) is defined as how much faster a parallel arrangement will get if compared with the same problem is solved with a single CPU. This law is a pure statistical description of the problem when all the multiple CPUs are supposed to be running at maximum capacity (i.e. 100%).

$$S(n) = \frac{1}{(1-p) + \frac{p}{n}}$$

(1)

When Amdahl put his observations the Main Frame vendors were discussing the possibility of work with multiple CPUs in parallel to scale up the processing power for customers. The result stopped the parallel CPUs approach. At that time the parallel ratio was estimated to be around 70%, leading to a maximum speed up of 3.33. With the single CPU approach wining, all the engineering efforts were put to develop CPUs increasingly powerful, pushing the engineers and scientists to keep in this direction for decades. What kept the industry drive was the *Moore's law*, that is an observation made by Gordon Moore, where the number of transistors roughly doubles in the integrated circuits every two years (MOORE, 1965). To unveil the potential of this claim one have to combine *Moore's law* with *Polllack's Rule* (POLLACK, 1999) that states that for a single core microprocessor the performance increases roughly proportional to the square root of the increase in its complexity. What leads a performance increase of about 40%, each two years, due to the doubling in number of logical ports.

However, recently Moore's law has been losing its momentum, generating a profound impact in the electronic and software industry. Conte (CONTE et al., 2015) has affirmed that: "Year-over-year exponential computer performance scaling has ended. Complicating this is

the coming disruption of the "technology escalator" underlying the industry: Moore's law. To fundamentally rethink and restart the performance-scaling trend requires bold new ways to compute and a commitment from all stakeholders".

New alternatives come in place to keep the law working, even "*artificially*", and the parallel processing via multiple CPUs working together came back again as a solution. But as we know the performance will not scale linearly with the number of CPU cores. Therefore, the characterization of the real performance of CPU cores running in parallel has become very important to keep the exponential growth escalator of Moore's law still working.

## 2.2.1 AMDAHL'S LAW AND SPEEDUP IN MULTI-CORE SYSTEMS

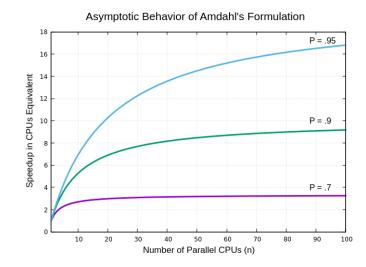

Amdahl's law presents an asymptotic behavior as shown in Figure 1 (speed-up for parallel ratios of p = 0.7, p = 0.9, p = 0.95 and p = 0.995). Equation 2 shows that the maximum speed-up depends only on the parallel ratio.

$$S(n)_{max} = \lim_{n \to \infty} S(n) = \lim_{n \to \infty} \frac{1}{(1-p) + \frac{p}{n}} = \frac{1}{(1-p)}$$

(2)

Figure 1: *Speedup* dependency on number of CPUs (*n*) and Parallel Ratio (*p*). Source: (Based on Equation 1)

Synthesizing this behavior, no matter how many parallel cores we have in a system, the overall speedup is limited to a maximum value, that is dependent on how efficiently parallelized the system can be.

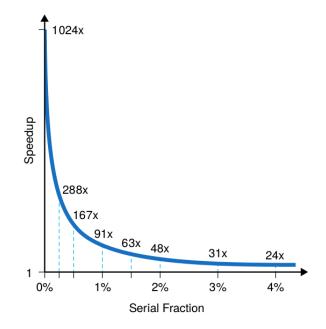

Figure 2: Asymptotic maximum *speedup* function of the serial ratio *s*. Source: ((GUSTAFSON, 1988))

Another way to see it is shown in Figure 2, where the maximum speedup is plotted as a function of the serial ratio *s*. Basically it plots the result of Equation 2 for each s = 1 - p. Note that when *s* is small, the speedup grows quickly, what is already expected since with a smaller *s* the more efficient is the parallel part of the system.

# 2.2.2 AMDAHL'S LAW COROLLARY - THE FIXED SIZE LAW APPLIED TO MULTI-CORE

To understand the consequences and the opportunities derived by Amdahl's Law when applied to multi-core architecture Hill and Marty (HILL; MARTY, 2008) have derived a corollary, where the micro-architecture of multi-core systems is further explored to refine the results of Amdahl's law in such environment. The speed-up reflects the timespan reduction when the task is running in a multi-core system compared to the same task running on a single core. For now we will explore this assumption to formulate the speedup for multi-core systems, but the reinterpretation of this assumption is the basis for the work of Gustafson (GUSTAFSON, 1988), that better explain the behavior of highly parallelized systems.

The formulation of the corollary starts with the assumption that a multi-core chip is formed by n cores, and each core can individually deliver a processing power of one BCE (Base Core Equivalent), meaning that all the cores are identical. At this point, the speedup is measured in BCEs, as one single core has one BCE, the speedup of a multi-core is the total amount of BCEs for a particular micro-architecture and this is limited to n BCEs (when the s = 0). The other assumption is that the architects can come up with more efficient systems that can treat the serial part with a performance that scales in the order of perform(r) (in other words, the sequential part can be seen as a single processor with r BCE processing power). In addition, if r BCEs are spent to the serial part treatment, the parallel part can scale up to m = n/r BCEs. According to Bokar (BORKAR, 2007) the serial performance can be considered  $perform(r) = \sqrt{r}$ , that is an assumption coherent to Pollack's Rule (POLLACK, 1999).

To continue the analysis, we have the definition of fixed size speed-up shown in Equation 3, meaning that the performance of the parallelized system (enhanced) is compared with the single core system (original). To calculate the speedup, the performances are calculated as the reciprocal of the execution times.

$$Speedup_{FS} = \frac{Enhanced \ Performance}{Original \ Performance} = \frac{T_{Original}}{T_{Enhanced}}$$

(3)

Considering that the task has a fixed size w, we have in consequence the execution times presented in Equations 4a and 4b:

$$T_{Original} = \frac{w}{perform(1)} \tag{4a}$$

$$T_{Enhanced} = Serial \ time + Parallel \ time = \frac{(1-p)w}{perform(r)} + \frac{Pw}{\frac{n}{r}.perform(r)}$$

(4b)

Combining Equation 3 with Equations 4a and 4b, we end up with a *Speedup*<sub>FS</sub> shown in Equation 5:

$$Speedup_{FS} = \frac{\frac{w}{perform(1)}}{\frac{(1-p)w}{perform(r)} + \frac{Pwr}{n.perform(r)}} = \frac{1}{\frac{1-p}{perform(r)} + \frac{p.r}{perform(r).n}}$$

(5)

This formulation seems unrelated to Amdahl's law, but if we consider that the enhanced system can deliver a constant performance perform(r) = c and that m = n/r, the Equation 5 becomes:

$$Speedup_{FS} = \frac{c}{(1-p) + \frac{p}{m}},$$

(6)

that is exactly the original Amdahl's law with the serial scaling of r BCEs and the parallel processing scaling of m BCEs.

That is why Equation 5 is a corollary of the original law. This result is important to send a message to micro-architects to develop multi-core systems that can handle the serial part more efficiently as well as support non blocking parallelization. This would lead to better performance. The great contribution of Hill and Marty work is the baseline to think in a more restrictive environment that is the micro-chips, where the degrees of freedom are diminished, due to topological and physical reasons.

#### 2.3 TIME FIXED LAW, THE GUSTAFSON'S LAW

The problem with Amdahl's law and its corollary is that it is too restrictive. Empirically we know that the performance scaling is not linear, but it is not as bad as the predictions we have so far. This was the point of start for Gustafson's work (GUSTAFSON, 1988) that observed it and conjectured that the fixed size approach is not dominant in modern architecture multi-CPUs. According to him literally: "We now have timing results for a 1024-processor system that demonstrate that the assumptions underlying Amdahl's 1967 argument are inappropriate for the current approach to massive ensemble parallelism." and "Yet for three very practical applications (s = 0.4 - 0.8 percent) used at Sandia, we have achieved the speedup factors on a 1024-processor hypercube which we believe are unprecedented: 1021 for beam stress analysis using conjugate gradients, 1020 for baffled surface wave simulation using explicit finite differences, and 1016 for unstable fluid flow using flux-corrected transport. How can this be, when Amdahl's argument would predict otherwise?"

Of course, the kind of interconnection architecture cited ("hyper-cube") is not easy, if not impossible, to reproduce in microprocessors that are essentially planar. However, he started an argumentation that puts more light on the study of the real behavior of the speedup that is more adherent to the actual state of art in microprocessors. It was proposed that the tacit assumption that the parallel workload p is fixed independently of the number of available cores N is not always true, but actually the problem size scales with the number of processors. It is because when a more powerful processor is used, the problem expands to the user to make use of the increased facilities (for example, grid resolution, number of time-steps, difference operator complexity, and other parameters) making the time to complete the task approximately constant. This assumption is know as Fixed Time and relaxed the Fixed Size assumed by Amdahl.

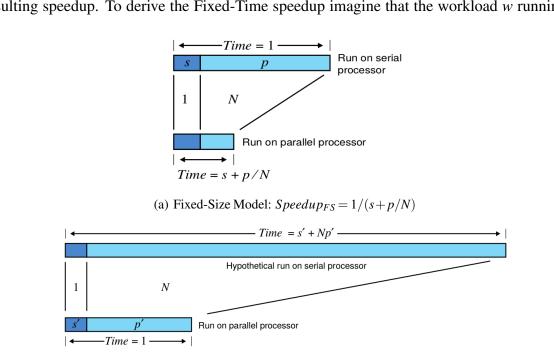

Figure 3(a) and Figure 3(b) shows both models, Fixed-Size and Fixed-Time, with the resulting speedup. To derive the Fixed-Time speedup imagine that the workload *w* running on

(b) Fixed-Time Model:  $Speedup_{FT} = s + Np$

# Figure 3: Scalability of Fixed-Size (Amdahl's law) and Fixed-Time Models (Gustafson's law). Source: (GUSTAFSON, 1988)

a single CPU scales up to w' on a multi-core processor, with the assumption that the time in each core is fixed (normalized to 1), we have thus w' = (1 - p)w + pNw. Equation 7 shows the *Speedup<sub>FT</sub>*, also known as Gustafson's Law:

$$Speedup_{FT} = \frac{Sequential \ Time \ of \ Solving \ w'}{Parallel \ Time \ of \ Solving \ w'} = \frac{Sequential \ Time \ of \ Solving \ w}{Sequential \ Time \ of \ Solving \ w}} = \frac{w'}{w}$$

$$= \frac{(1-p)w + pNw}{w} = (1-p) + Np = s + Np$$

(7)

Equation 7 suggests that there is a linear scaling of speedup that we know is not true, but shows better results when considering experimental data. So something is missing on this law, that will be explained in the next section, with a refination of this model, known as Sun and Ni's law (or Memory Bounded Model). From now, it is important to get a better understanding of the techniques to calculate the scaling, so we will have the arsenal to understand next section.

For example, if n = r in Equation 5 the speedup is equal to perform(r), this is used as

the initial condition for the analysis that follows. Now if n = mr is the scaled number of cores to be used in the fixed time model approach (that assumes the scaling is only in the parallel portion) thus w' = mw, then we have the total workload:

$$\frac{(1-p)w}{perform(r)} + \frac{pw}{perform(r)} = \frac{(1-p)w}{perform(r)} + \frac{pw'}{perform(r)m}$$

(8)

Comparing Equation 8 with the scaling of serial part, that is the initial situation where n = r, we have:

$$Speedup = \frac{Sequential Time of Solving w'}{Sequential Time of Solving w} = \frac{\frac{(1-p)w}{perform(r)} + \frac{pw'}{perform(r)m}}{\frac{w}{perform(r)}} = (1-p) + mp$$

(9)

To analyse what Equation 9, if we consider a situation where 1024 cores are working in parallel, and considering p = 0.99 in fixed time model, we will have a speedup of about 10. On the fixed-time model it jump to about 1013. What is behind the assumption of a fixed time model is that there are always room for more work to process in the parallel processing part. To illustrate it, let's see what happens when we escalate the parallel part during the scaling up the number of cores:

$$Total Work = Serial Work + Parallel Work = (1-p)w + pw' = [1 + (m-1)p]w$$

(10)

Once the parallel work is escalated, compared with the total work calculated by Equation 10, the new parallel ratio p' is shown on Equation 11:

$$p' = \frac{mfw}{[1 + (m-1)p]w} = \frac{p}{\frac{1}{m} + \frac{m-1}{m}p}$$

(11)

If  $m \to \infty$  in Equation 11, then  $p' \to 1$ , showing that the serial part is less and less important in the scaling process.

### 2.4 MEMORY BOUND MODEL, THE SUN AND NI'S LAW

The Gustafson's assumption that the parallel part scales up to meet a fixed time bound is not always true, and Sun and Ni (SUN; NI, 1990) observed that the parallel scaling problem was related to the memory scaling capabilities of the systems. This is a natural approach, if we take the assumption that it is impossible to put infinite resources in the chip, so there is a bounding in the scaling capabilities of the computational system imposed usually by memory limitations.

Sun and Ni proposed the Memory Bound Model, for that they defined the *Speedup<sub>MB</sub>* as shown in Equation 12, where  $w^*$  is the scaled workload under a memory space constraint, in other words the *memory is bounded*.

$$Speedup_{MB} = \frac{Sequential \ Time \ of \ Solving \ w^*}{Parallel \ Time \ of \ Solving \ w^*}$$

(12)

If we assume that a single core is a pair *processor-memory*, once we scale up the number of cores, the memory will also scales up. Letting y = g(x) represents the parallel part p, the workload increases when the memory capacity increases for a factor of m. Implicating that w = g(M) and  $w^* = g(m.M)$ , with M being the amount of memory for one processor-memory pair. We can say that  $w^* = g(m.g^{-1}(w))$ . Thereby Equation 13 shows the generic *speedup*<sub>MB</sub> for any g(x).

$$Speedup_{MB} = \frac{(1-p)w + p.g(m.g^{-1}(w))}{(1-p)w + \frac{p.g(m.g^{-1}(w))}{m}}$$

(13)

It is important to say that g(x) is a function that depends on the application running in the computational system, because it reflects the scaling that the memory experiments when running the application, that is essentially connected with the essence of the algorithm being used by the application. In other words, scaling is function of the kind of application running. It is confirmed by the empirical data collected for the present work.

The generic formulation of Memory Bound Model was further developed by Sun and Ni considering that there are many algorithms with polynomial complexity, and usually this complexity is fully characterized using only the highest term of the polynomial. This way, considering  $g(x) = a.x^b$ , with  $a, b \in \mathbb{Q}$ . Thus we can say that  $g(m.x) = a(m.x)^b = m^b.a.x^b = m^b.g(x)$ , now calling  $m^b = \overline{g}(m)$  as a power function with degree of 1. Equation 13 becomes Equation 14 that is also know as *Sun and Ni's Law*.

$$Speedup_{MB} = \frac{(1-p)w + p.\bar{g}(m)w}{(1-p)w + \frac{p.\bar{g}(m)w}{m}} = \frac{(1-p) + p.\bar{g}(m)}{(1-p) + \frac{p.\bar{g}(m)}{m}}$$

(14)

To gain insight on what Equation 14 represents and how to use it, consider the situation where the application to be studied is an algorithm for matrix multiplication. The complexity of this algorithm when solved by brute force is polynomial with degree 3, actualy  $y = 2N^3$  with

N meaning the dimension of the two NxN matrices being multiplied. We can say that  $x = 2N^3$  what leads to  $g(N) = 2(\sqrt{\frac{x}{3}})$  and  $\bar{g}(x) = x^{\frac{1}{2}}$ . Puting these results on Equation 14, we have the Equation 15:

$$Speedup_{MB} = \frac{(1-p) + p\bar{g}(m)}{(1-p) + \frac{p\bar{g}(m)}{m}} = \frac{(1-p) + p.m^{\frac{1}{2}}}{(1-p) + p.m^{\frac{1}{2}}}$$

(15)

This clearly is not the linear scaling predicted by Fixed Time Model. If we consider the work-flow scaling in Memory Bound as  $w^*$  and in Fixed Time as w', if each element of the matrix that is stored in memory is used at least one time, then  $w^* \ge w'$  what leads to  $Speedup_{MB} \ge Speedup_{FT}$ . In fact Gustafson's law is a particular case when  $\bar{g}(m) = m$ .

Initially this is good news for the multi-core solution, but there is a drawback, as said before, there is a physical limitation with the amount of memory available and the access time to treat this scaling problem, it is know as *memory wall problem* (WULF; MCKEE, 1995). In simplistic words, one can say that there is no room in local memory (specially caches) to guarantee the locality (cache hits) during all the execution time. This means that, delays to retrieve all the needed data plus instructions plays important role when the size of the problem grows. To take it in account in the next session the memory wall is considered in the model.

## 2.5 MEMORY WALL PROBLEM

The access time to memory has big impact on performance. Over the time, this impact has became much worse, because when we compare the access time to memory with respect with the clock cycle period, it has increased several orders of magnitude. It has certainly decreased in terms absolute values, but relative to the clock cycle (that dictates the instruction execution pace) it increased significantly. For example, in 1980 the memory latency was about 0.3 cycles of clock, in 2005 this value has jumped to 220 cycles of clock.

To mitigate this effect and improve the performance of the CPUs, memory caches were aggregated into the CPU chips. In multi-core chips, caches are distributed alongside the cores. These cache memories are much faster than normal memories, but they are much smaller because of manufacturing costs and chip space. This approach works well because it relies on the locality of the software, meaning that must of the time processors are executing repeatedly a small segment of instructions and data. For example, most of the time the algorithms are executing "for loops".

But this architecture has a drawback, if the information needed is not in the cache, the processor first look it in the cache, receiving a cache miss information, and only after screening all cache levels ( $L_1$ ,  $L_2$  and  $L_3$ ) it is allowed to seek the information in the external memory. It makes the external memory access even slower. This architecture is usually more efficient than not using caches. However, in highly parallel systems, if we don't have enough cache to respond to the scaling of the problem size, it can create a bottleneck to the CPU scaling for the parallel tasks.

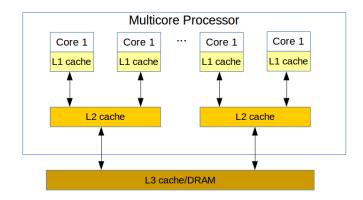

Figure 4 shows the memory organization in multi-core systems, caches  $L_1$  are the closer to the core,  $L_2$  caches can be shared among pair of cores.  $L_3$  cache can exist or not, if not existing it is the external memory (usually DRAM).

Figure 4: Typical Memory Organization in Multi-core Systems.

The diminishing CPU scaling due to lack of cache in multi-cores is known as the *memory wall problem*, first introduced by Wulf (WULF; MCKEE, 1995). To have an idea of how this impacts the system scaling, an Intel i7-6500U implements  $L_3$  cache size of 4096kB,  $L_2$  caches with size of 256kB and  $L_1$  caches with size of 32kB. It has basically the same core architecture of a Xeon E7-8890 v4, nevertheless Xeon will have 60MB for  $L_3$  cache, 4MB for  $L_2$  and  $L_1$  caches. But Xeon scales much better then i7, being a processor of choice for Servers and specialized systems, with i7 being more suitable to personal computer systems.

The *memory wall* scaling can be modeled using the same approach used to model Fixed Time and Memory Bound speedups. In this case we assume that the total work for a task is composed of two parts, the data processing work  $w_p$  and the data communication (access) work  $w_c$ , and  $w = w_p + w_c$ . If assumed that  $w_c$  is independent of the workload and independent of the total workload (what is reasonable since the memory access time and the lines of code are The same independently to the number of cores for a particular situation), and  $w_c$  is function of r and supposing the scaling of the number of cores from r to mr, as per Memory Bound model we will have :

$$Speedup_{MB} = \frac{\frac{w_c}{perform(r)} + \frac{pw_p^*}{perform(r)}}{\frac{w_c}{perform(r)} + \frac{pw_p^*}{m.perform(r)}} = \frac{w_c + pw_p^*}{w_c + \frac{pw_p^*}{m}} = \frac{w_c + p.g(m.g^{-1}(w_p))}{w_c + \frac{p.g(m.g^{-1}(w_p))}{m}}$$

(16)

In Equation 16, if g(x) is rational, we have the simplification bellow:

$$Speedup_{MB} = \frac{w_c + p.\bar{g}(m).w_p}{w_c + \frac{p.\bar{g}(m).w_p}{m}}$$

(17)

Equation 17 can be compared with Equation 14 to have an idea of the memory wall impact over the speedup due to the effect of memory scaling and latency. What we see is that  $w_c$  dominates the serial workout, meaning that the scaling of  $w_p$  can reach a saturation. This leads to an obvious conclusion, if is to put effort to keep improving the hardware efficiency, research in memory improvements should be a focal point.

First of all, it is important to say that all these models are essentially right if they have their assumptions met. The models were constructed to speculate and further advance the knowledge on what is important and what can be neglected for parallel computing, regarding the CPU scaling. In addition, these models give a ground to think where to concentrate efforts in architecture research and development to extract the best performance. However, these models are not enough to calculate a real world scaling problem, because they were created to give general answers and to support benchmarking. In the next chapter we will address a model form Kandalintsev and Lo Cigno (LO CIGNO; KANDALINTSEV, 2012), that was developed to address the problem of predicting the real scaling based on measured coupling factors.

#### **3 PERFORMANCE MODELING**

# 3.1 MODELING FOR PERFORMANCE PREDICTION

In the previous chapter we saw statistical laws that help to understand the performance, in terms of CPU scaling, considering the time-span divided in two parts, the serial and the parallel ratio. This was useful to understand the play role of the macro components (architectural and software design) and the impacts on the overall system performance. However, in practice, the execution ratios are not known beforehand, and they are not easily measured, since they are dependent on the nature of hardware design and its interaction with the software it is running. This opens the necessity for models and tools capable to predict the performance based on the behavior of some components. There are several of such tools and models, according to Kunkel et. al. (KUNKEL et al., 2000) they usually fit in two types, *cycle-accurate models* and *high-level models*. Unfortunately, for the research goals none of these approaches are good fits, because our idea is to have a performance model capable to assist on real time decisions made by the Operating System or a Resource Management software.

Bellow we describe one *cycle-accurate model* and one *high-level model*, it will give us a good ground to understand why the BFO model proposed by Kandalintsev and Lo Cigno is better suited for our purposes.

#### 3.1.1 RPM - HIGH-LEVEL MODEL

RPM (Rapid Prototyping Engine) (BARROSO et al., 1995) is a *high-level model* tool designed to multi-core prototyping. It is based on a hardware emulation of the processor. It is build using FPGA (Field Programmable Gate Array) to build the cache, memory, coherence and communication controllers, and some off-the-shelf components including processors, SRAMs, DRAMs, FIFOs, bus interface and drivers, and backplane.

The idea is to put the original processor served with the FPGA services instead of the internal cache or the coherence and communication controllers. This way it is possible to register the statistics of events not accessible in multi-core processors, that are crucial to model the performance behavior in a very accurate way. This approach is very powerful to benchmark one architecture running a real application. However, RPM emulates the cache operations 80 times slower than the original computational system.

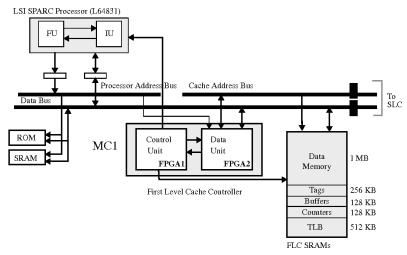

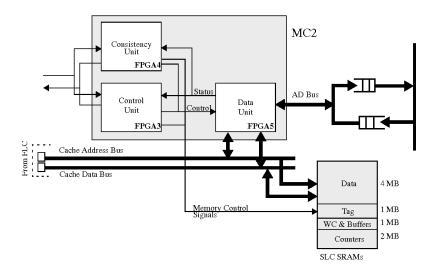

Figures 5 and 6 shows the First-Level Cache (FLC) and Second-Level Cache (SLC) implementation for RPM. In Figure 5, the FLC controller is implemented in FPGA1 and FPGA2 (in Memory Controller 1 (MC1)), they connect to the Address and Data Bus of the processor, in this case a SPARC L64831. When the processor read the L1 cache, the cache controller answer in Data Bus in case of a cache hit, otherwise it seek for the SLC using the cache controller Address Bus. Figure 6 details the SLC controller architecture. Again, if the there is a cache hit, Memory Controller 2 (MC2) deliver the data segment to MC1 (it is based on a send/receive protocol implemented in hardware). In case of cache miss, the SLC controller will seek for a new segment in the external memory. This is a known process, but the details of implementation can be studied to improve the performance.

Moreover, the FLC and SLC controllers work in a different clock, usually 8 times faster than the processor clock (*pclock*). It is useful to get the details of the process and study the intermediate states. However, the FPGA maximum clock is usually less than the processor maximum clock, usually in a factor of 10, and added to it *pclock* is set 8 times slower than the FPGA clock, it means that this setup runs 80 times slower than the processor in a production environment. It makes this approach, very usefull for prototyping and benchmarking, but not usefull for real time performance measurements.

The same approach, high level emulation, is implemented by several authors/tools. For example Eyerman et. al. (EYERMAN; EECKHOUT, 2009), developed a methodology to study SMT (Simultaneous Multi-Thread) processors. It uses the same approach of RPM in a sense that the cache study is central in the analysis. However, modern multi-core processors have internal counters that can be read in real time, making it possible to infer the relevant statistics, instead of directly measuring it as RPM does.

Anyways, besides very accurate, these models are time consuming and not suitable for real time decisions. They best fit for benchmark, as stated in the introductory paragraph of the

The processor and its first-level cache

Figure 5: RPM First-Level Cache (FLC) implementation diagram; it shows the L1 cache implemented in FPGA and the Bus coherence to access L2 cache (refer to Figure 6 for details). Source: (BARROSO et al., 1995)

Figure 6: RPM Second-Level Cache (SLC) implementation diagram; it shows the L2 cache implemented in FPGA and the Bus controller to access external Memory (AD Bus). Source: (BARROSO et al., 1995)

section.

## 3.1.2 SLATE - CYCLE-ACCURATE MODEL

SLATE (System-Level Analysis Tool for Early Exploration) (BERGAMASCHI et al., 2007) is a tool based on a methodology that models the CPU core internals, based on execution and wait times, in a queue driven analysis. It is based on SystemC performance modeling, that consists on the description of the model to be simulated in terms of components (caches, queues, cores and interconnection between them). In each component it is associated the times.

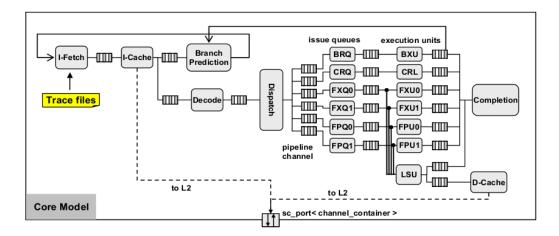

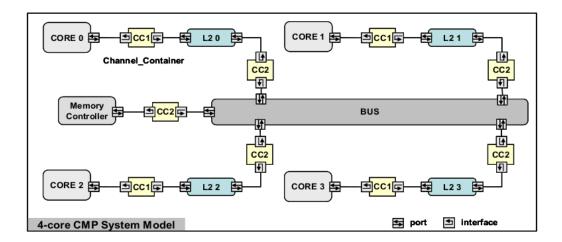

For example, cores have execution time and caches have wait times (associated to the time to make the data available). Figure 7 and Figure 8, shows a complete Power4 CPU modeling. The Power 4 is a quad-core, single thread, single instruction CPU, with L2 and L1 caches implemented. In Figure 7 it is modeled a single core and its components (decode, dispatch, issue queues, execution units, and so on). All are modeled in high-level in terms of delays and execution times, and the engine calculates cycle by cycle the state of the system (that is why it is cycle accurate model). The modeled core is then used as the building block of the model in Figure 8, where are modeled the interconnections and the controls of the multi-core environment.

Figure 7: Internal Organization of Core Model - Power4 single core modeled. Source: (BERGAMASCHI et al., 2007)

Figure 8: Internal Organization of 4-Core System Model - Power4 CPU modeled. Source: (BERGAMASCHI et al., 2007)

Cycle-accurate models are useful to prototype the CPU design, to predict the behavior of the architecture under test with predefined applications modeled in terms of load and size. It is not suitable to our purposes, since our idea is to simulate the multi-core performance scaling of commercial processors and not prototype a new processor.

#### 3.1.3 THE BEHAVIORAL FIRST ORDER (BFO) CPU PERFORMANCE MODEL

In Kandalintsev's PhD Thesis "Application Interference in Multi-Core Architectures: Analysis and Effects" (KANDALINTSEV, 2016), Chapter 3 is dedicated to explain the BFO model conceptually and mathematically. He observes that it is well known that the interference between cores plays an important role in multi-core processors, for example, Burger et. al. (BURGER et al., 1996) explains how the velocity gap between processor speed and memory access has increased and the consequences in performance of processing, similar work is developed by Carvalho et. al. (CARVALHO, 2002) pointing that performance of modern CPUs are dependent on the performance of internal cache that are shared by the cores. Xu et. al. (XU et al., 2012) studied how to minimize the impact of the interference among the cores studying algorithms to provide fairness in the use of caches.

Based on a inter-core interference interpretation, Kandalintsev proposed a model that studies the decrease in performance of a CPU core, due to concurrency with others CPU cores for common shared resources. It models the observable behavior, the increase in execution time when the CPU core is competing with others for shared resources, comparing with the situation where the CPU core presents no concurrency. The model defines the extra time to complete a job when concurrency is present as *overhead* (*OH*).

The model proposes that the overhead will be measured when the CPU cores under test are fully occupied (100% load), but admits that the actual *OH* is a function of the actual load in the CPU cores. In other words, if the CPU cores are using less than 100% of capacity, they will have lesser probability to find some resource already occupied. This assumption is compatible with the Amdahl's law corollary, where the speed-up of multi-core systems are better than the Amdahl's law predicts (in terms of BCEs) if the actual utilization is lower than what is available in the processor. In fact it is expected that the serial ratio be lowered by the performance function perf(n) and it is accepted to be  $perf(n) = \sqrt{n}$  by experience, being *n* the actual amount of BCEs demanded.

Starting now with the formal definitions of the model we have:

- 1. *Assumptions:* The overhead is present when there are tasks running in parallel, otherwise there is no overhead. The model considers steady state performance (meaning tasks that run for long time), examples are video encoding, scientific simulations and data streaming. It is assumed that the dominant interaction between tasks is pairwise, i.e., the total overhead is the sum of the overhead running in pairs. The expectation here is to have the overhead overestimated, but still a good approximation of the real system.

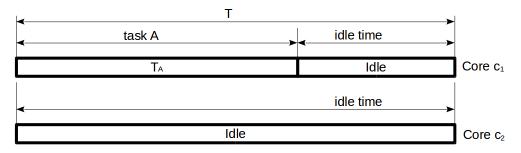

- 2. Definitions and Notation: The task load,  $L_i = L(T_i)$  with  $L_i \in [0, 1]$ , is defined as the time required by task *i* in a particular CPU core, assuming that the CPU core can be running several tasks in time shared way. The total load per-core is the sum of the task loads and sum up to a maximum of 1. Figure 9 presents a graphical view of load task and how to calculate it. *N* is defined as the number of CPU cores.  $L_{sys}$  is the normalized system load

|                | Observation time T |        |      |           |                |  |  |  |

|----------------|--------------------|--------|------|-----------|----------------|--|--|--|

| task 1         | task 2             | task 1 | task | idle time | task           |  |  |  |

|                |                    |        | 3-   |           | 2              |  |  |  |

| T <sub>1</sub> | T <sub>2</sub>     | T1     | Тз   | Idle      | T <sub>2</sub> |  |  |  |

The load task  $L_i$  is the sum of the times task i uses the CPU core during the observation time T. It is normalized with respect to T, this way  $L_i = \Sigma_i(T_i)/T$

#### Figure 9: Task Load definition: Tasks schedule in one CPU core in one slice of time T.

and is defined as the sum of total loads of all CPU cores in the system;  $L_{sys} \in [0, N]$ . The pipe notation  $T_i|T_j$  denotes that the tasks  $T_i$  and  $T_j$  are running in different CPU cores. Using pipe notation we have  $L_{sys}(A|B)$  being the normalized system load when task A is running in one CPU core and task B in another CPU core.

$$L_{sys}(A|B) = L_A + L_B + L_{A|B}^{oh}$$

(18)

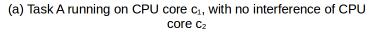

$L_{A|B}^{oh}$  is the parasitic load caused by task A running in one CPU core and task B running in another CPU core. This is maybe the most essential part of the model and reflects the waiting time where one CPU core has to stop the execution of a task because of a busy common resource, extending the execution time. The idea is that this extended execution time is enough to model the interaction and make dependable predictions. In Figure 10 it is shown the interpretation of the  $L_{A|B}^{oh}$ , where it can be seen that the interaction is only present when there are tasks running in parallel on both CPU cores. The formal definition

(b) Task A running on CPU core  $c_1$  is interfered by task B running on CPU core  $c_2$ .

Figure 10: Interference between tasks running on different cores. (a) Task A running on CPU core c1, with no interference of CPU core c2, (b) Task A running on CPU core c1 is interfered by task B running on CPU core c2.

of  $L_{A|B}^{oh}$  is derived by the equation 19,

$$\mathcal{L}_{A|B}^{oh} = \beta_{A|B} \mathcal{L}_A \mathcal{L}_B \tag{19}$$

where  $\beta_{A|B}$  expresses the level of interference (or coupling) that task A running in one CPU core and task B running in another CPU core exert on each other. This interference is assumed to be constant and dependent only on the nature of the tasks itself. If two tasks have affinity to the same resources, is expected to be higher than if the tasks have different affinities. Equation 19 shows  $L_{A|B}^{oh}$  as function of  $\beta_{A|B}$  that represents the interference due to the nature of the tasks, and the product of the individual loads. The idea behind it is to map the amount of time where the interference actually works as the product of the individual loads.

One could think that  $\beta$  could make more explicit the internals of the processors and peripherals. It could be done considering it as a vector, and each component would refer

to one common resource, like a FPU (Floating Point Unit) that is shared with two cores or because the cores are hyper-threaded, same for ALU (Arithmetic and Logic Unit) and this analysis would be extended to caches, memory, disk, I/O, etc. The problem with it is that this vector would be like 40 or even 50 components long (TANG et al., 2007), it would greatly increase the complexity of the model.

In order to overcome this problem the overhead load function is decomposed in individual performance penalties related to each task,

$$\mathcal{L}_{A|B}^{oh} = \beta_{A \to B} \mathcal{L}_A \mathcal{L}_B + \beta_{B \to A} \mathcal{L}_A \mathcal{L}_B \tag{20}$$

where  $\beta_{A\to B}$  represents the interference of task A over task B and  $\beta_{B\to A}$  represents the interference of task B over task A.

The same formulation can be expressed in matrix notation, by Equations 21 and 22, or in shorten form by equation 23,

$$\beta_{A \to B} L_A L_B = \begin{bmatrix} L_A & 0 \end{bmatrix} \begin{pmatrix} \beta_{A \to A} & \beta_{A \to B} \\ \beta_{B \to A} & \beta_{B \to B} \end{pmatrix} \begin{bmatrix} 0 \\ L_B \end{bmatrix}$$

(21)

$$\beta_{B \to A} L_B L_A = \begin{bmatrix} 0 & L_B \end{bmatrix} \begin{pmatrix} \beta_{A \to A} & \beta_{A \to B} \\ \beta_{B \to A} & \beta_{B \to B} \end{pmatrix} \begin{bmatrix} L_A \\ 0 \end{bmatrix}$$

(22)

$$L_{1\to2}^{oh} = \mathbf{T}_1^T \mathbf{B} \mathbf{T}_2 \tag{23}$$

where **B** is the matrix of  $\beta$ -coefficients, **T**<sub>1</sub> and **T**<sub>2</sub> are vectors that represents the task running on CPU core 1 and 2, respectively, and  $L_{1\rightarrow2}^{oh}$  is the overhead that the tasks running on CPU core 1 impose to the tasks running on CPU core 2. This matrix representation is very useful because usually the CPU cores are running threads that sometimes have the same kind of task, specially in some kind of servers, like database, web-services or specialized services. In this matrix formulation the diagonal has the interference effect of threads of one kind of task over threads of same kind but running in different CPU cores.

A further generalization can be formulated to calculate the pairwise overhead with the

two CPU cores running a multitude of tasks, lets say *n* CPU cores and *m* tasks. Equations 24 and 25 show this generalized formulation,

$$L_{sys}^{oh} = L_{c1\rightarrow c2}^{oh} + L_{c1\rightarrow c3}^{oh} + \dots + L_{c1\rightarrow cn}^{oh} + L_{c2\rightarrow c1}^{oh} + L_{c2\rightarrow c3}^{oh} + \dots + L_{c2\rightarrow cn}^{oh} + \dots + L_{cn\rightarrow c1}^{oh} + L_{cn\rightarrow c2}^{oh} + \dots + L_{cn\rightarrow cn-1}^{oh} = \sum_{i=1}^{n} \sum_{\substack{j=1\\j\neq i}}^{n} \mathbf{T}_{i}^{T} \mathbf{B} \mathbf{T}_{j}$$

$$(24)$$

where the overhead imposed on CPU core ci, running m tasks from t1 to tm, by the interference of CPU core cj, running the same tasks, is calculated by:

$$L_{ci \to cj}^{oh} = \beta_{t1 \to t2} L_{t1}^{i} L_{t2}^{j} + \beta_{t1 \to t3} L_{t1}^{i} L_{t3}^{j} + \dots + \beta_{t1 \to tm} L_{t1}^{i} L_{tm}^{j} + \beta_{t2 \to t2} L_{t1}^{i} L_{t2}^{j} + \beta_{t2 \to t3} L_{t2}^{i} L_{t3}^{j} + \dots + \beta_{t2 \to tm} L_{t2}^{i} L_{tm}^{j} + \beta_{tm \to t2} L_{tm}^{i} L_{t2}^{j} + \beta_{tm \to t3} L_{tm}^{i} L_{t3}^{j} + \dots + \beta_{tm \to tm} L_{tm}^{i} L_{tm}^{j}$$