# UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁ ENGENHARIA DE CONTROLE E AUTOMAÇÃO

# DIEGO ROCHA GUEDES HUGO LEONARDO OLIVEIRA DA CUNHA

# SÍNTESE DE CONTROLADORES ROBUSTOS APLICADOS EM SISTEMAS COM ATRASOS TEMPORAIS

TRABALHO DE CONCLUSÃO DE CURSO

CORNÉLIO PROCÓPIO 2018

# DIEGO ROCHA GUEDES HUGO LEONARDO OLIVEIRA DA CUNHA

# SÍNTESE DE CONTROLADORES ROBUSTOS APLICADOS EM SISTEMAS COM ATRASOS TEMPORAIS

Trabalho de Conclusão de Curso apresentado ao Curso Superior de Engenharia de Controle e Automação da Universidade Tecnológica Federal do Paraná como requisito parcial para obtenção do título de Engenheiro de Controle e Automação.

Orientador: Prof. Dr. Cristiano Marcos Agulhari

Coorientador: Prof. Dr. André Sanches Fonseca Sobrinho

# Universidade Tecnológica Federal do Paraná Campus Cornélio Procópio Departamento Acadêmico de Elétrica Curso de Engenharia de Controle e Automação

# **FOLHA DE APROVAÇÃO**

# **Diego Rocha Guedes**

# Síntese de controladores robustos aplicados em sistemas com atrasos temporais

Trabalho de conclusão de curso apresentado às 13:30hs do dia 07/06/2018 como requisito parcial para a obtenção do título de Engenheiro de Controle e Automação no programa de Graduação em Engenharia de Controle e Automação da Universidade Tecnológica Federal do Paraná. O candidato foi arguido pela Banca Avaliadora composta pelos professores abaixo assinados. Após deliberação, a Banca Avaliadora considerou o trabalho aprovado.

| Prof(a). Dr(a). Cristiano Marcos Agulhari - Presidente (Orientador) |

|---------------------------------------------------------------------|

| Prof(a). Dr(a). André Sanches Fonseca Sobrinho - (Coorientador)     |

| Prof(a). Dr(a). Luiz Francisco Sanches Buzachero - (Membro)         |

| Prof(a) Dr(a) Emerson Bayazzi Pires da Silva - (Membro)             |

# Universidade Tecnológica Federal do Paraná Campus Cornélio Procópio Departamento Acadêmico de Elétrica Curso de Engenharia de Controle e Automação

# **FOLHA DE APROVAÇÃO**

# Hugo Leonardo Oliveira da Cunha

# Síntese de controladores robustos aplicados em sistemas com atrasos temporais

Trabalho de conclusão de curso apresentado às 13:30hs do dia 07/06/2018 como requisito parcial para a obtenção do título de Engenheiro de Controle e Automação no programa de Graduação em Engenharia de Controle e Automação da Universidade Tecnológica Federal do Paraná. O candidato foi arguido pela Banca Avaliadora composta pelos professores abaixo assinados. Após deliberação, a Banca Avaliadora considerou o trabalho aprovado.

| Prof(a). Dr(a). Cristiano Marcos Agulhari - Presidente (Orientador) |

|---------------------------------------------------------------------|

| Prof(a). Dr(a). André Sanches Fonseca Sobrinho - (Coorientador)     |

| Prof(a). Dr(a). Luiz Francisco Sanches Buzachero - (Membro)         |

| Prof(a). Dr(a). Emerson Ravazzi Pires da Silva - (Membro)           |

#### **RESUMO**

GUEDES, Diego Rocha; CUNHA, Hugo Leonardo Oliveira. **Síntese de controladores robustos aplicados em sistemas com atrasos temporais**. 2018. 105 f. Trabalho de Conclusão de Curso (Graduação) – Engenharia de Controle e Automação. Universidade Tecnológica Federal do Paraná. Cornélio Procópio, 2018.

Este trabalho visa o estudo, desenvolvimento e aplicação da síntese de uma técnica de controle robusto para sistemas afetados por atrasos temporais. A formulação envolve uma abordagem via Desigualdades Matriciais Lineares (do inglês Linear Matrix Inequalities - LMI) em um problema de otimização convexa, incorporando Reguladores Quadráticos Lineares (do inglês Linear-Quadratic Regulators - LQR), para que se minimize um custo garantido associado ao controle do sistema. O desenvolvimento baseia-se em uma técnica de síntese que já foi apresentada na literatura, que considera atrasos nos estados de um sistema incerto, tendo agora a contribuição deste trabalho com a extensão da síntese para o caso em que há também atrasos nas entradas de controle. A resolução do problema de otimização é feita na plataforma MATLAB, e o resultado fornece ganhos estabilizantes, por realimentação de estados, e com custo garantido otimizado. É apresentada também a implementação do controlador em um sistema embarcado, em que um microcontrolador da família PIC18 é responsável por controlar a velocidade de um servomotor, enquanto que atrasos propositais são inseridos na comunicação entre os dispositivos, a fim de testar e validar a técnica de síntese desenvolvida.

**Palavras-chave:** Sistemas com atrasos temporais, Controle de custo garantido, Controle Robusto, Desigualdades Matriciais Lineares (*LMIs*), Reguladores Quadráticos Lineares (*LQR*).

#### **ABSTRACT**

GUEDES, Diego Rocha; CUNHA, Hugo Leonardo Oliveira. **Synthesis of robust controllers applied in time-delayed systems**. 2018. 105 p. Course Conclusion Work (Graduation) – Control and Automation Engineering. Federal University of Technology - Parana. Cornélio Procópio, 2018.

This work aims the study, development and application of the synthesis of a robust control technique for time-delayed systems. The synthesis is modeled by a LMI approach in the formulation of a convex optimization problem, incorporating LQR, so that the guaranteed cost associated with the control system is minimized. The development is based on a synthesis technique already presented in the literature that considers delays in the states of an uncertain system, being the greatest contribution of this work the extension of the synthesis to the case of delayed inputs. The resolution of the optimization problem is performed on the MATLAB platform, and provides stabilizing state feedback gains with an optimized guaranteed cost. A physical implementation of the controller on an embedded system is also presented, composed of a microcontroller of the PIC18 series, responsible for controlling the speed of a servomotor, while intentional delays are inserted in the communication between the devices in order to test and validate the developed synthesis technique.

**Keywords:** Time Delayed Systems, Guaranteed Cost Control, Robust Control, Linear Matrix Inequalities (LMIs), Linear Quadratic Regulators (LQR).

# **LISTA DE FIGURAS**

| Figura 1 – Conjuntos convexos e não convexos                               | 19 |

|----------------------------------------------------------------------------|----|

| Figura 2 – Kit didático 2208 DATAPOOL                                      | 28 |

| Figura 3 – Kit didático XM118 EXSTO                                        | 29 |

| Figura 4 – Pinagem do PIC 18F4550                                          | 30 |

| Figura 5 – Dispositivo DAQ NI-6008                                         | 32 |

| Figura 6 – Circuito para identificação do sistema do servomecanismo        | 33 |

| Figura 7 – Esquemático de funcionamento                                    | 38 |

| Figura 8 – Esquemático do circuito                                         | 38 |

| Figura 9 – Esquemático do vetor pilha                                      | 40 |

| Figura 10 – Valores de RB1 medidos pelo Osciloscópio                       | 41 |

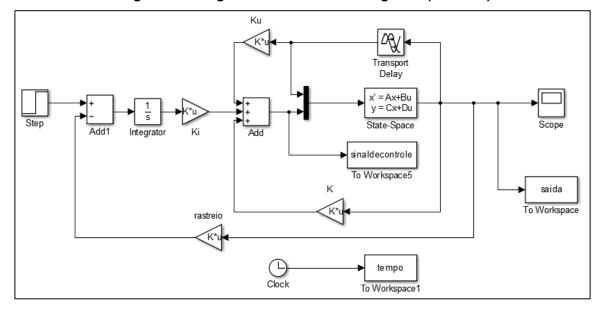

| Figura 11 – Esquemático de Sistema com atraso nos estados e na entrada de  |    |

| controle (Simulink)                                                        | 57 |

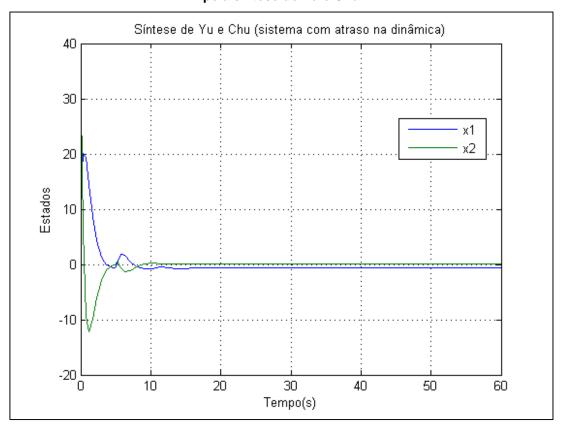

| Figura 12 – Simulação do sistema exemplo com atraso na dinâmica com ganhos |    |

| calculados pela síntese de Yu e Chu                                        | 58 |

| Figura 13 - Simulação do sistema exemplo com atraso na dinâmica e na       |    |

| entrada de controle com ganhos calculados pela síntese de Yu e Chu         | 59 |

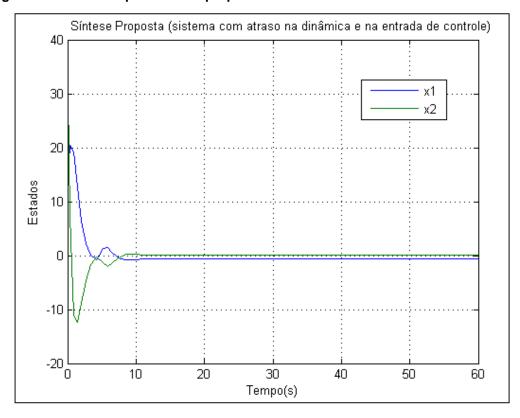

| Figura 14 - Simulação do sistema exemplo com atraso na dinâmica e na       |    |

| entrada de controle com ganhos calculados pela síntese proposta            | 60 |

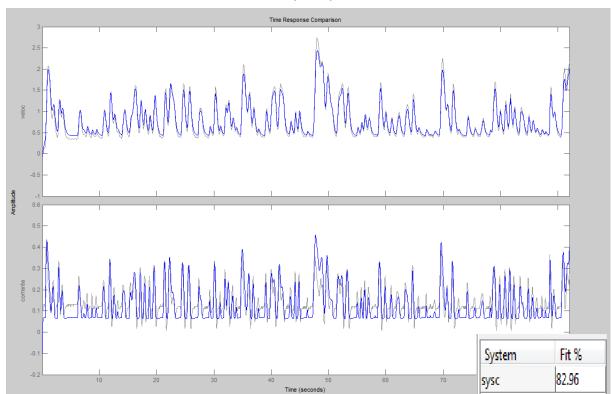

| Figura 15 – Comparação de resposta do sistema estimado com a resposta do   |    |

| sistema real                                                               | 62 |

| Figura 16 – Diagrama de blocos com integrador (Simulink)                   | 64 |

| Figura 17 – Simulação do modelo matemático do servomotor para 0,408s de    |    |

| atraso                                                                     | 65 |

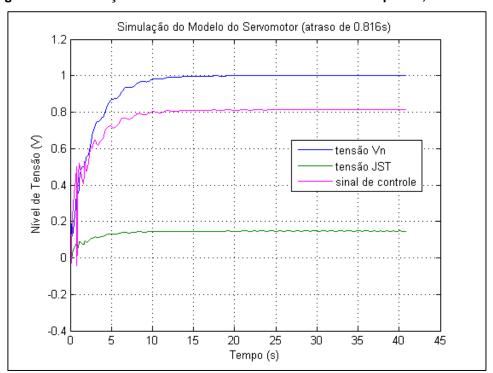

| Figura 18 - Simulação do modelo matemático do servomotor para 0,816s de    |    |

| atraso                                                                     | 65 |

| Figura 19 – Dados recebidos pela comunicação serial                        | 66 |

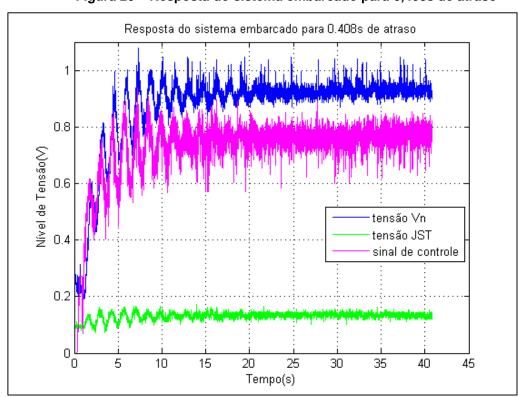

| Figura 20 – Resposta do sistema embarcado para 0,408s de atraso            | 67 |

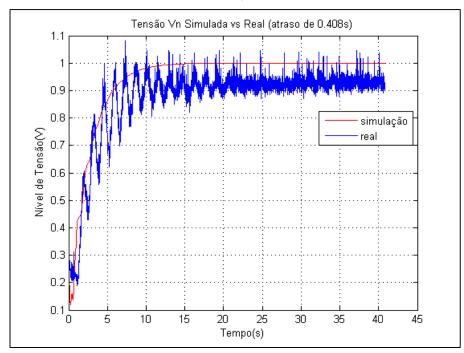

| Figura 21 – Comparação entre tensão Vn e simulada para atraso de 0,408s    | 68 |

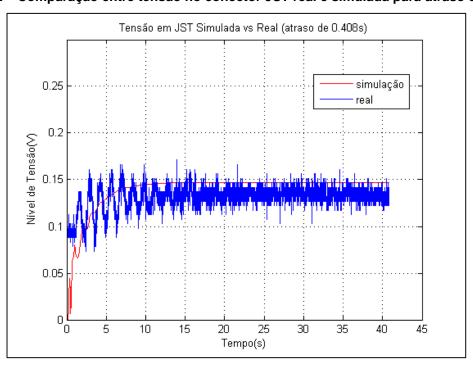

| Figura 22 - Comparação entre tensão no conector JST real e simulada para   |    |

| atraso de 0,408s                                                           | 68 |

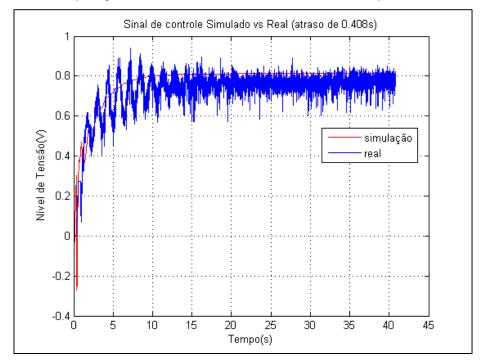

| Figura 23 – Comparação entre sinal de controle real e simulado para atraso de |    |

|-------------------------------------------------------------------------------|----|

| 0,408s                                                                        | 69 |

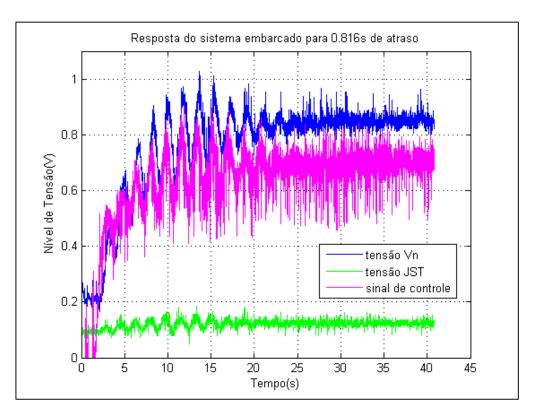

| Figura 24 – Resposta do sistema embarcado para 0,816s de atraso               | 70 |

| Figura 25 - Comparação entre tensão Vn real e simulada para atraso de         |    |

| 0,816s                                                                        | 71 |

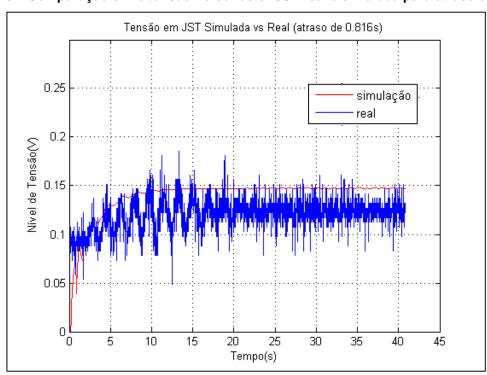

| Figura 26 - Comparação entre tensão no conector JST real e simulada para      |    |

| atraso de 0,816s                                                              | 71 |

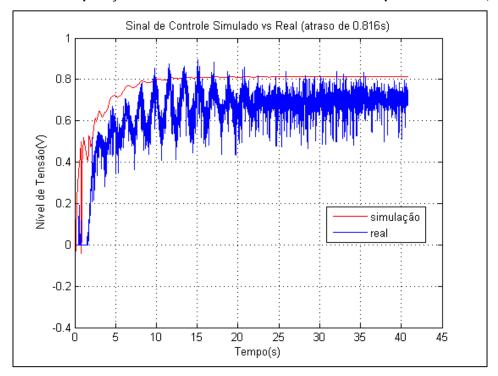

| Figura 27 – Comparação entre sinal de controle real e simulado para atraso de |    |

| 0,816s                                                                        | 72 |

|                                                                               |    |

# **LISTA DE QUADROS**

| Quadro 1 – Descrição dos pinos do PIC18F4550 | 30 |

|----------------------------------------------|----|

|----------------------------------------------|----|

# SUMÁRIO

| 1     | INTRODUÇÃO 12                                            |    |  |  |  |

|-------|----------------------------------------------------------|----|--|--|--|

| 1.1   | Justificativa                                            | 13 |  |  |  |

| 1.2   | Problematização1                                         |    |  |  |  |

| 1.3   | Objetivo geral 1                                         |    |  |  |  |

| 1.4   | Objetivos específicos 1                                  |    |  |  |  |

| 2     | FUNDAMENTAÇÃO TEÓRICA1                                   |    |  |  |  |

| 2.1   | Estabilidade de Lyapunov                                 | 16 |  |  |  |

| 2.2   | Problemas de Otimização Via Análise Convexa              | 18 |  |  |  |

| 2.3   | Desigualdades Matriciais Lineares                        | 20 |  |  |  |

| 2.4   | Complemento de Schur                                     | 21 |  |  |  |

| 2.5   | Incertezas Paramétricas Limitadas em Norma               | 21 |  |  |  |

| 2.6   | Reguladores Quadráticos Lineares                         | 23 |  |  |  |

| 2.7   | Ação Integral                                            | 23 |  |  |  |

| 2.8   | Implementação Física – Microcontrolador PIC              | 24 |  |  |  |

| 2.8.1 | Sinal PWM                                                | 24 |  |  |  |

| 2.8.2 | Conversor A/D                                            |    |  |  |  |

| 2.8.3 | Comunicação Serial Assíncrona2                           |    |  |  |  |

| 3     | MATERIAIS E MÉTODOS 2                                    |    |  |  |  |

| 3.1   | Servomecanismo                                           | 27 |  |  |  |

| 3.2   | Microcontrolador PIC 18F4550                             | 28 |  |  |  |

| 3.3   | Placa DAQ NI-6008                                        | 32 |  |  |  |

| 3.4   | Plataforma MATLAB                                        | 33 |  |  |  |

| 3.4.1 | Identificação do Modelo Matemático do Kit Servomecanismo | 33 |  |  |  |

| 3.4.2 | Construção e Resolução das LMIs                          | 35 |  |  |  |

| 3.4.3 | Simulação dos controladores via Simulink                 | 37 |  |  |  |

| 3.5   | Funcionamento do Projeto Embarcado 3                     |    |  |  |  |

| 3.5.1 | Estruturação do Atraso Temporal                          |    |  |  |  |

| 3.5.2 | Aquisição de dados4                                      |    |  |  |  |

| 3.5.3 | Geração da saída de controle                             | 42 |  |  |  |

| 3.5.4 | Transmissão de dados                                     | 44 |  |  |  |

| 4     | RESULTADOS E DISCUSSÕES                                  | 46 |  |  |  |

| 4.1                                | Síntese para Sistemas com Atraso nos Estados                   | 46  |  |  |

|------------------------------------|----------------------------------------------------------------|-----|--|--|

| 4.2                                | Desenvolvimento de Síntese para Sistemas com Atraso nos        |     |  |  |

|                                    | Estados e na Entrada de Controle                               | 50  |  |  |

| 4.3                                | Simulação das Sínteses Abordadas 56                            |     |  |  |

| 4.4                                | Modelo Matemático em Espaço de Estados do Servomecanismo 61    |     |  |  |

| 4.5                                | Geração dos Ganhos de Controle e Simulação para Modelo         |     |  |  |

|                                    | Matemático do Servomecanismo                                   | 62  |  |  |

| 4.6                                | Resultados obtidos para a implementação física                 | 66  |  |  |

| 5                                  | CONSIDERAÇÕES FINAIS                                           | 74  |  |  |

| REFER                              | RÊNCIAS                                                        | 75  |  |  |

| ANEX                               | O I – Código para identificação do modelo em Espaço de Estados |     |  |  |

| do Ser                             | vomotor                                                        | 78  |  |  |

| ANEX                               | O II – Código para síntese de ganho dos controladores          | 81  |  |  |

| ANEX                               | O III – Código do firmware                                     | 85  |  |  |

| ANEX                               | O IV – Código para separação de dados da comunicação serial    | 91  |  |  |

| ANEX                               | O V – Registradores conversor A/D                              | 93  |  |  |

| ANEXO VI – Registradores sinal PWM |                                                                |     |  |  |

| ANEX                               | O VII – Registradores Comunicação Serial Assíncrona            | 101 |  |  |

# 1 INTRODUÇÃO

Sistemas de controle são estruturas que manipulam, a partir de um controlador, os atuadores de um sistema físico para que este sistema apresente um comportamento final pré-determinado. Entretanto, sistemas físicos nem sempre possuem dinâmicas triviais devido a diferentes possíveis interferências, como as causadas pela própria integração do controlador no sistema. No projeto de controladores, mesmo quando os sistemas propostos são contínuos no tempo, a sua implementação é feita em geral através de dispositivos digitais que inevitavelmente geram atrasos de comunicação (SIMEÃO, 2009)

Outro fator a ser considerado ao projetar controladores para plantas reais é de que, além de ser necessário assegurar a estabilidade do sistema proposto, também é apropriado considerar questões relativas ao desempenho adequado para o controlador. Assim, existe a necessidade de projetar uma técnica que resulte em controladores cujos ganhos apresentem grandezas coerentes à realidade e que sejam capazes de otimizar parâmetros pré determinados do sistema. Neste trabalho essa necessidade é suprida através dos Reguladores Quadráticos Lineares (do inglês *Linear Quadratic Regulators - LQR*). Tais questões foram anteriormente estudadas por Chang e Peng (1972), quando esse conceito fora estabelecido pela primeira vez como controle com custo garantido, e permanecendo em uso como é notado em Yu e Chu (1999), Leite et al. (2007), Miranda et. al (2008), Guedes et. al (2017) bem como nas referências usadas por estes.

Esse tratamento leva em conta o fator de desempenho e as possíveis alterações devido à presença de incertezas na dinâmica do sistema, delimitadas por um limite superior pré-determinado. As incertezas citadas podem ser oriundas de diversas fontes, como por variações de parâmetros, dinâmicas que não foram previamente modeladas ou por presença de atrasos de comunicação entre as partes de um sistema. Para o projeto proposto por este trabalho, são consideradas as incertezas que podem ser estruturadas entre limites físicos, conhecidas como incertezas limitadas em norma.

#### 1.1 Justificativa

É perceptível que atrasos temporais são encontrados nos mais diversos âmbitos de aplicação. Em processos biológicos, por exemplo, atrasos nas dinâmicas dos sistemas modelados podem surgir pelo tempo de condução do sistema nervoso, tempo de maturação em populações celulares e animais e tempo circulatório no sistema cardiovascular (MACDONALD, 1989). Em sistemas de engenharia, Kolmanovskii e Myshkis (1999) citam aplicações em reatores químicos e nucleares, controle de curso de navio e laminação de metais. Além desses, há também os sistemas com atrasos temporais envolvidos em redes de comunicação de dados, como sistemas de tráfegos de veículos e sistemas de teleoperação (NICULESCU, 2001).

O presente trabalho é uma proposta de síntese de controladores que tratam dessa classe de sistemas. Dessa forma, se baseando na técnica desenvolvida por Yu e Chu (1999), que apenas considera atrasos nos estados do sistema, os autores deste trabalho desenvolvem - como pode ser visto no artigo de mesmo nome publicado no Simpósio Brasileiro de Automação Inteligente de 2017 - uma adaptação da técnica capaz de lidar com incertezas na entrada de controle. Além da construção da nova abordagem, também são apresentados os resultados e análises de uma implementação física, utilizando dos kits didáticos Módulo 2208 – Servomecanismo, da empresa DATAPOOL, e XM118 - Banco de Ensaios em Microcontroladores PIC18F. O servomecanismo tem seu sistema devidamente identificado e, através do PIC18F, o controlador é estabelecido.

# 1.2 Problematização

Sistemas com incertezas paramétricas são frequentemente abordadas por técnicas de controle robusto, que são baseadas no uso de funções de Lyapunov, como a caracterização da estabilidade quadrática, por exemplo. Boyd et al. (1994) foi um dos precursores na modelagem destas técnicas a partir de resoluções por

desigualdade matriciais lineares (do inglês *Linear Matrix Inequalities - LMIs*), que é uma importante ferramenta para formulação de problemas em sistemas de controle capaz de ser resolvida computacionalmente por um algoritmo de otimização convexa sempre que existir uma solução possível para o problema proposto. Dessa maneira, quando isso ocorre, a estabilidade do sistema é assegurada e o custo garantido é otimizado quando uma solução factível é encontrada para o conjunto de *LMIs* que representam as condições propostas pela síntese de controle.

Estes sistemas recebem uma atenção considerável na literatura pois, como já dito, atrasos em sistemas reais sempre foram características frequentes, seja devido a propriedades intrínsecas do sistema ou por consequência da própria ação de controle. Além de serem frequentes, estes atrasos temporais também impactam negativamente a estabilidade dos sistemas. Assim, a abordagem através das funcionais de Lyapunov-Krasovskii (Kolmanovskii et al, 1999), desenvolvidas por meio de *LMIs*, se apresentam como uma proposta de análise que atesta a estabilidade robusta dos sistemas.

# 1.3 Objetivo Geral

Para este trabalho, tem-se como objetivo desenvolver um controlador robusto capaz de tratar das incertezas limitadas em norma e atrasos temporais nos estados do sistema e na realimentação do controlador, garantindo ainda um custo de controle otimizado. Técnicas que consideram atrasos na entrada são pouco exploradas na bibliografia atual, cabendo citar Mukaidani (2003) pelo qual fora o único trabalho encontrado desenvolvendo, de forma distinta, um técnica de síntese que considere tal atraso.

Como dito, tal síntese já havia sido implementada por Yu e Chu (1999) sem a consideração de atrasos temporais na entrada de controle, portanto esse trabalho se trata de uma contribuição à síntese desenvolvida por estes, além de possibilitar uma aplicação prática da técnica, que permite a validação de sua eficiência

# 1.4 Objetivos Específicos

- Estudar e projetar técnicas de síntese de controladores robustos aplicadas a sistemas com incertezas limitadas em norma e atrasos temporais;

- Desenvolver condições LMIs para otimizar o custo de ganho de controle considerando atrasos temporais nos estados e na entrada de controle;

- Aplicar a síntese de controle desenvolvida em um sistema físico composto de um kit didático Módulo 2208 – Servomecanismo, da empresa DATAPOOL;

- Utilizar o kit didático XM118 Banco de Ensaios em Microcontroladores

PIC18F para desenvolvimento da malha de controle do sistema;

- Validar o desempenho da técnica desenvolvida a partir de testes no sistema embarcado projetado.

# 2 FUNDAMENTAÇÃO TEÓRICA

Neste capítulo são abordados os conceitos utilizados para desenvolvimento da técnica de síntese proposta. Dessa forma serão esclarecidos alguns conceitos como Desigualdades Matriciais Lineares (*LMIs*), que é a abordagem matemática utilizada para resolução do problema que visa minimizar o custo garantido de um sistema com atraso temporal nos estados e na entrada de controle. Por fim são apresentados aspectos da implementação física pretendida, com uma breve introdução sobre microcontroladores PIC.

# 2.1 Estabilidade de Lyapunov

A análise de estabilidade representa um papel central em teoria de sistemas e engenharia. Existem diferentes tipos de problemas de estabilidade no estudo de sistemas dinâmicos (SCHERER; WEILAND, 2005), sendo que, para o presente trabalho, refere-se à estabilidade no sentido Lyapunov, descrita a seguir.

Lyapunov foi um matemático e engenheiro russo que desenvolveu a teoria que hoje carrega seu nome. Sua principal contribuição foi redefinir o conceito de estabilidade, estabilidade assintótica e instabilidade de sistemas dinâmicos, além de estabelecer um método de verificação dessas propriedades em termos de existência das chamadas funções de Lyapunov (SCHERER; WEILAND, 2005). Os métodos de Lyapunov também podem ser utilizados para encontrar limitantes para critérios de desempenho definidos para um sistema (BOYD et al., 1994).

Inicialmente, considere o sistema

$$\dot{x}(t) = f(x(t)), \ x(t) \in \mathbb{R}^n, \ f(0) = 0.$$

(1)

Seja  $x_e$  um ponto de equilíbrio do sistema (1), e D um domínio de x(t) contendo  $x_e$ . O sistema (1) é estável em uma vizinhança  $\beta(x_e, \rho)$  em torno de  $x_e$  com raio  $\rho$ , se existir uma função contínua  $V: \mathbb{R}^n \to \mathbb{R}$  com derivadas contínuas em relação a t, tal que:

$$(i) \quad V(x(t)) \ge 0;$$

$$(ii) \quad V(x(t)) > 0 \text{ em } D - \{x_e\};$$

$$(iii) \quad \dot{V}(x(t)) \le 0 \text{ em } D.$$

$$(2)$$

A função V(x(t)) que satisfaz o conjunto de condições (2) é chamada função de Lyapunov. Ainda cabe dizer que se  $\dot{V}(x(t)) < 0$  em  $D - \{x_e\}$ , então o sistema é assintoticamente estável para a vizinhança  $\beta(x_e,\rho)$  (KHALIL, 2002). Dessa forma, qualquer trajetória de x(t),  $t \geq 0$ , tende a se aproximar arbitrariamente de  $x_e$  quando  $t \to \infty$ . E, por último, a função V(x(t)) é dita radialmente ilimitada se  $\|x(t)\| \to \infty$  implica em  $V(x(t)) \to \infty$ .

Estendendo a análise anterior, se para todo  $x(t) \in \mathbb{R}^n$ , V(x(t)) satisfaz o conjunto de condições (2), se V(x(t)) for radialmente ilimitada, e  $\dot{V}(x(t)) < 0$ , o sistema é globalmente assintoticamente estável (KHALIL, 2002).

Considere agora um sistema na forma

$$\dot{x}(t) = Ax(t),\tag{3}$$

em que  $A \in \mathbb{R}^{n \times n}$ . Uma condição necessária e suficiente para estabilidade do sistema (3) é a existência de uma função quadrática V(x(t)) = x'(t)Px(t), P > 0 que atende o conjunto de condições (2). Se a existência de P é garantida, diz-se que o sistema (3) é quadraticamente estável e V é chamada Função de Lyapunov Quadrática.

# 2.2 Problemas de Otimização via Análise Convexa

Um problema de otimização envolve a especificação das soluções candidatas e da formalização do conceito de decisão ótima para um problema proposto (SCHERER; WEILAND, 2005). Seja T o conjunto de todas as decisões possíveis em um problema de otimização, e H um subconjunto de T que contém todas as decisões factíveis (ou candidatas) de tal problema. A abordagem que visa quantificar o desempenho das soluções factíveis  $y \in H$  expressa os valores na forma J(y), em que  $J: H \to \mathbb{R}$  é uma função de valores reais chamada função objetivo ou função de custo. O valor das decisões  $y \in H$  é dado por J(y).

A partir da interpretação da função de custo, deseja-se minimizar ou maximizar os valores de *J* dentre todas as candidatas. Dessa forma, a decisão ótima se caracteriza como um elemento de *H* que minimize ou maximize *J* dentre todas as alternativas factíveis.

Em um problema de minimização, deve-se atenção a alguns fatores, como não assumir como solução ótima global candidatas que representam na verdade mínimos locais de J(y) (um erro comum em métodos numéricos), ou, se existe uma solução ótima, verificar se ela é única, e, caso contrário, escolher a solução que melhor se enquadra à realidade do problema.

A vantagem de uma análise em conjuntos convexos, ou funções convexas em um problema de otimização é a ausência de mínimos locais (SCHERER; WEILAND, 2005). Um conjunto *H* em um espaço vetorial linear é dito convexo se

$$\{y_1, y_2 \in H\} \Rightarrow \{y \coloneqq \sigma y_1 + (1 - \sigma)y_2 \in H, \forall \sigma \in (0, 1)\}. \tag{4}$$

Em termos geométricos, para quaisquer dois pontos em um conjunto convexo, o segmento de reta que os conecta deve pertencer a esse mesmo conjunto, como ilustrado pela Figura 1.

Figura 1 – Conjuntos convexos e não convexos

Fonte:https://pt.wikipedia.org/wiki/Conjunto\_convexo

De maneira semelhante, uma função  $J: H \to \mathbb{R}$ , é dita convexa se H é um conjunto convexo não vazio e se para todo  $y_1, y_2 \in H$  e  $\sigma \in (0,1)$ , têm-se

$$J(\sigma y_1 + (1 - \sigma)y_2) \le \sigma J(y_1) + (1 - \sigma)J(y_2). \tag{5}$$

Ainda, J é dita estritamente convexa se a desigualdade (5) é válida para todo  $y_1, y_2 \in H$ , sendo  $y_1 \neq y_2$ , e todo  $\sigma \in (0,1)$ .

Por fim, considerando J convexa, e supondo  $y_0 \in H$  como uma solução ótima local de J, então para todo  $y \in H$ , e  $\sigma \in (0,1)$  suficientemente pequeno,

$$J(y_0) \le J(y_0 + \sigma(y - y_0)) = J((1 - \sigma)y_0 + \sigma y) \le (1 - \sigma)J(y_0) + \sigma J(y), \quad (6)$$

que implica em

$$0 \le \sigma(J(y) - J(y_0)),\tag{7}$$

ou  $J(y_0) \le J(y)$ . Assim, toda solução ótima local de J é também uma solução ótima global se a função J(y), bem como o conjunto H, forem convexos. E então, se J for estritamente convexa,  $y_0$  é solução única (SCHERER; WEILAND, 2005).

# 2.3 Desigualdades Matriciais Lineares

Desigualdades Matriciais Lineares (*LMIs*) foram primeiro introduzidas por volta de 1890 por Lyapunov, quando este as usou para provar a estabilidade quadrática de um sistema dinâmico. Entretanto, só foram largamente exploradas como ferramentas de resolução de problemas da engenharia a partir da década de 1960. Desde a década de 1970, tornou-se ferramenta poderosa em teoria de sistemas e controle, uma vez que as *LMIs* originadas da área podem ser formuladas como problemas de otimização convexa, acessíveis para resolução computacional (BOYD et al., 1994).

Em termos matemáticos, uma LMI é uma expressão na forma

$$F(z) \coloneqq F_0 + \sum_{i=1}^m z_i F_i < 0, \tag{8}$$

em que  $z \in \mathbb{R}^m$  é um vetor de números reais chamados de variáveis de decisão,  $F_i = F_i' \in \mathbb{R}^{mxm}$ , i = 0, ..., m são matrizes simétricas reais e o símbolo de desigualdade em (8) significa "definida-negativa". Há também *LMIs* na forma não estritamente negativas como

$$F(z) \le 0. \tag{9}$$

É comum encontrar problemas em que ambos os tipos estão presentes.

# 2.4 Complemento de Schur

Como descrito na subseção 2.3, uma *LMI* pode estar nas formas (8) e (9). Quando uma *LMI* não se encontra nessas formas as desigualdades são não-lineares. Para estes é comum utilizar transformações ou outras desigualdades conhecidas na literatura para que as condições se tornem *LMIs*.

Desigualdades não-lineares, desde que sejam convexas, podem ser convertidas para a forma de *LMIs* utilizando complementos de Schur (BOYD et al., 1994). Sendo assim, considere as desigualdades não-lineares convexas

$$C > 0, \quad A - BC^{-1}B' > 0;$$

(10.1)

ou

$$A > 0$$

,  $C - B'A^{-1}B > 0$ . (10.2)

A LMI

$$M = \begin{bmatrix} A & B \\ B' & C \end{bmatrix} > 0 \tag{11}$$

é o equivalente pelo complemento Schur das desigualdades (10.1) e (10.2).

# 2.5 Incertezas Paramétricas Limitadas em Norma

Modelos matemáticos de sistemas físicos são frequentemente representados na forma de espaço de estados, em que suas componentes

representam quantidades físicas bem definidas. Entretanto, variações, perturbações ou incertezas em tais parâmetros físicos levam à incerteza do modelo.

Como pequenas variações podem ter um impacto considerável na dinâmica de um sistema, faz-se necessário considerar essas perturbações no projeto de controladores. Visto que a natureza e extensão dessas incertezas atuando em um sistema pode ser parcialmente ou totalmente conhecida, durante a construção do modelo matemático utiliza-se uma inclusão de termos diferenciais lineares (do inglês *Linear Differential Inclusions*, ou *LDI*) (BOYD et al., 1994). Essas inclusões estão divididas em pelo menos dois casos distintos: incertezas paramétricas invariantes no tempo e incertezas paramétricas variantes no tempo (SCHERER; WEILAND, 2005). Neste trabalho, os atrasos temporais atuantes em um sistema dinâmico foram incluídos no modelo matemático na forma de incertezas paramétricas variantes no tempo e limitadas por norma.

Seja  $\delta = [\delta_1 \dots \delta_n]'$  o vetor que contém as incertezas do sistema. Suponha que seus elementos são desconhecidos e limitados por norma. Considere o sistema

$$\dot{x}(t) = A(\delta)x(t) + B(\delta)u(t), \tag{12}$$

afetado pelas incertezas  $\delta$ . A representação do sistema (12) com as incertezas limitadas por norma é dada por

$$\dot{x}(t) = (A + \Delta A)x(t) + (B + \Delta B)u(t), \ \Delta(\cdot) = DF(t)E(\cdot) \tag{13}$$

em que F(t) é uma função matricial desconhecida, na forma de um bloco diagonal  $diag(\delta_i I_{ni})$  e  $|\delta_i| \le 1$ , satisfazendo  $F'(t)F(t) \le I$ . As matrizes D e E são matrizes conhecidas que indicam as direções de entrada de F(t).

# 2.6 Reguladores Quadráticos Lineares

A fim de otimizar o custo de controle de um sistema dinâmico através de critérios de desempenho, é possível utilizar os Reguladores Quadráticos Lineares (do inglês *Linear Quadratic Regulators*, ou *LQR*).

O LQR é uma técnica para cálculo de um ganho por realimentação de estados que minimiza a função de custo associado ao sistema. Um sistema dinâmico contínuo no tempo na forma (12), possui uma função de custo

$$J = \int_0^\infty [x'(t)Qx(t) + u'(t)Ru(t)]dt, \qquad (14)$$

em que *Q* e *R* são matrizes simétricas positivas-definidas com a finalidade de ponderar, respectivamente, a velocidade com que os estados atingem seu valor de regime permanente e a energia de controle atuante (KWAKERNAAK; SIVAN, 1972).

# 2.7 Ação Integral

A ação integral tem por objetivo eliminar o erro em regime estacionário entre o valor de resposta de um sistema e sua referência. Isso acontece porque a componente integral soma o termo de erro ao longo do tempo, em intervalos regulares, de forma que mesmo um erro pequeno faz com que a componente integral aumente lentamente. Assim sendo, a resposta integral irá aumentando ao longo do tempo a menos que o erro seja nulo, conduzindo o erro em regime permanente para zero.

O sinal do integrador é dado pela equação (15)

$$I = K_i \int_0^t e(\tau) d\tau, \tag{15}$$

em que  $K_i$  é o ganho integral e  $e(\tau)$  é o erro entre a referência e a resposta do sistema.

# 2.8 Implementação Física – Microcontroladores PIC

Os microcontroladores PIC (*Peripheral Integrated Controler*) são fabricados pela *Microchip Tecnology* e baseiam-se na arquitetura Harvard, com conjunto de instruções no modelo RISC. Possuem barramento de dados de 8 *bits*, e barramento de instruções divididos em famílias de 12, 14 e 16 *bits*.

Entre os principais periféricos (variando de acordo com o modelo) estão: Conversores analógico-digitais, contadores (*timers*) de 8 e 16 *bits*, comparadores analógicos, USARTs, controladores de comunicação (I²C, SSP e USB), controladores PWM, controladores LCD, controladores Ethernet, *watchdog timer*, portas digitais com capacidade de 25 mA, entre outros. Os periféricos utilizados neste projeto terão mais atenção nas seções subsequentes.

O microcontrolador abordado na proposta de trabalho é o PIC18F4550 da família PIC 18 de microcontroladores 16 *bits*. Para tanto, utiliza-se de um *kit* didático fabricado pela *EXSTO*, no modelo MX118. Os detalhes do *kit* podem ser conferidos no Capítulo 3.

#### 2.8.1 Sinal PWM

Sinais PWM, do inglês *Pulse Width Modulation*, nada mais são do que sinais de onda quadrada com período fixo e largura de pulso variável. A razão entre a largura do pulso em estado lógico alto e o período do sinal é definido como ciclo de

trabalho, mais conhecido pela sua tradução livre para o inglês: *duty cycle*. E a frequência do sinal é equivalente ao inverso do período. Todavia, esses dois parâmetros são os responsáveis por estabelecer o sinal PWM.

Os módulos CCPx são responsáveis pela geração deste sinal e necessitam de uma base de tempo para ditar a sua frequência. Para tal, o CCPx utiliza o TIMER2 - outro periférico do PIC em questão. Os registradores associados aos módulos requisitados são CCPRxL, CCPRxH, CCPxCON, PR2 e T2CON - disponíveis da seção ANEXO deste trabalho, e são através destes que são feitas as configurações necessárias.

Para a definição do período, isto é, o inverso da frequência do sinal, utilizase da seguinte equação:

$$T_{PWM} = (PR2 + 1) \times 4 \times T_{OSC} \times PS \tag{16}$$

Onde:

$T_{PWM}$  = Período do PWM;

PR2 = Registro de comparação do Timer2;

$T_{OSC}$  = Período de um clock do oscilador externo;

PS = Pré-escala do TMR2

Já o *duty cycle*, como mencionado, é definido pela razão do tempo do pulso em nível alto e o período do sinal:

$$DC = \frac{tp}{T} = \frac{[CCPRxL\ CCPxCON < 5:4>]}{(PR2+1)\times 4}$$

(17)

# 2.8.2 Conversor A/D

Converter sinais analógicos em sinais digitais com amplitudes correspondentes dependem diretamente de conceitos como quantização e taxa de

amostragem. O primeiro estabelece a escala de valores, em bits, que a amplitude do sinal poderá ser representada. Já o segundo determina a frequência em que as amostras são coletadas. Essa frequência, segundo o teorema de amostragem, deve ser pelo menos duas vezes maior que a frequência do sinal que está sendo convertido, para que ele possa ser reconstruído com fidelidade (PEREIRA, 2010).

O PIC18F4550 possui um conversor de 10bits, com 13 canais, intitulado como ADC (do inglês *Analog-to-Digital Convert*). Ele é o responsável por converter a tensão lida em um dos canais em uma palavra binária. Os parâmetros necessários para a sua configuração são as tensões de referência,  $V_{ref+}$  e  $V_{ref-}$  que determinam os valores de tensão máximo e mínimo, e o tempo de digitalização das amostras - definidos pelo clock de conversão ( $T_{AD}$ ) e tempo de aquisição ( $T_{ACQ}$ ). Os registradores associados à configuração necessária são ADCON0, ADCON1 e ADCON2, também anexados a esse trabalho.

# 2.8.3 Comunicação Serial Assíncrona

Em uma comunicação serial assíncrona os dados são transmitidos em forma de caracteres padronizados pelo código ASCII (do inglês *American Standard Code for Information Interchange*), de um transmissor para um receptor. Sendo assim, uma palavra binária correspondente ao caractere em questão é enviado sequencialmente em um mesmo meio físico para o seu destino. No PIC18F4550 a interface que define o padrão físico e elétrico do dispositivo de comunicação é a norma RS-232C.

O módulo EUSART (do inglês *Enhanced Universal Synchronous/Asynchronous Receiver/Transmitter*) do PIC em uso é um dos responsáveis pela configuração dessa comunicação. Os registradores envolvidos na operação são TXSTA, RCSTA e BAUDCON. E, por fim, para a delimitação da velocidade de comunicação é necessária a escolha do BRG (do inglês *Baud Rate Generator*) que deverá ser armazenado nos registradores SPBRGH e SPBRG.

# **3 MATERIAIS E MÉTODOS**

Neste capítulo são apresentados os materiais necessários para a implementação do sistema físico a ser controlado pela técnica de controle desenvolvida. Além disso, também são relatados os métodos utilizados para a construção e execução do trabalho. Para tanto, faz-se necessário uma introdução sobre sistemas dinâmicos afetados por atrasos temporais. Um sistema do tipo  $\dot{x}(t) = Ax(t)$ , quando afetado por atrasos é dado na forma

$$\dot{x}(t) = Ax(t) + A_1x(t-d) \tag{18}$$

em que d representa o tamanho do atraso afetando o sistema,  $A_1$  representa uma matriz de dinâmica atrasada, x(t) são as variáveis de estado atuais e x(t-d) representam as variáveis de estado atrasadas.

Dessa forma o controle por realimentação de estados retorna os sinais de controle u(t)=Kx(t) e  $u(t-d)=K_ux(t-d)$ , sendo esse último resultante da técnica de síntese proposta neste trabalho. Os sinais de controle apresentados representam a entrada de controle atual e a entrada de controle atrasada do sistema.

#### 3.1 Servomecanismo

O sistema físico proposto para implementação do controlador desenvolvido é o *kit* didático Módulo 2208 – Servomecanismo, da empresa DATAPOOL, que possibilita a análise da posição e/ou da velocidade angular do servo motor. Tal equipamento possui transdutores de rotação (tacômetro) e sensores de deslocamento (servo-potenciômetros) para medirem as dinâmicas citadas com

seus respectivos sinais já devidamente condicionados internamente ao *kit* para funcionarem entre tensões de 0 a 5V e correntes de 0 a 20mA (DATAPOOL, 2006).

O motor empregado nesse *kit* didático é um servo motor de corrente contínua que sofre intervenção na sua tensão de armadura, através de um *driver* com sinais de comando responsáveis pela ação de controle. Os sinais de controle do motor também funcionam entre tensões de 0 a 5V e correntes de 0 a 20mA que, por sua vez, são convertidas pelo *driver* para sinais de atuação de tensões e correntes de +/- 12V e 1,5 A, respectivamente.

Esses sistemas ainda possuem variáveis K1 e K2 que geram distúrbios causados por variações do torque, que podem ser tratadas como incertezas paramétricas pela técnica de controle proposta. A Figura 2 ilustra o *kit* didático.

Figura 2 – Kit didático 2208 DATAPOOL

Fonte: Datapool Eletrônica Ltda

#### 3.2 Microcontrolador PIC 18F4550

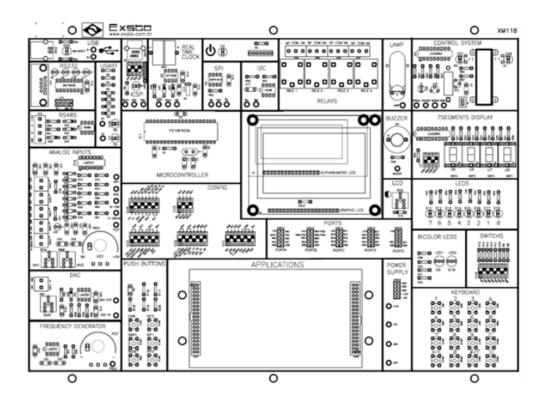

Para a comunicação entre os componentes do sistema físico, bem como para a construção lógica da técnica de controle para o desenvolvimento do projeto, será utilizado o *kit* didático XM118 - Banco de Ensaios em Microcontroladores PIC18F. A Figura 3 apresenta o esquemático do *kit*.

Figura 3 - Kit didático XM118 EXSTO

Fonte: Manual do Kit (EXSTO)

Este *kit* é baseado no PIC18F4550, mencionado anteriormente. Sua tensão de alimentação é da ordem de 4 a 5,5 V e, dada uma frequência de operação de 48MHz, ele chega a ser capaz de executar até 12 milhões de instruções por segundo (MIYADAIRA, 2009).

O condicionamento do sinal não se faz necessário, uma vez que cada pino de entrada/saída do microcontrolador possui tensão de 5V em nível lógico alto, e corrente máxima de 20 mA (valores condizentes para aplicação do sinal de controle no servomotor). Esses valores de tensão e corrente serão condicionados internamente ao *driver* como mencionado anteriormente. A seguir, a Figura 4 ilustra a pinagem do PIC18F4550.

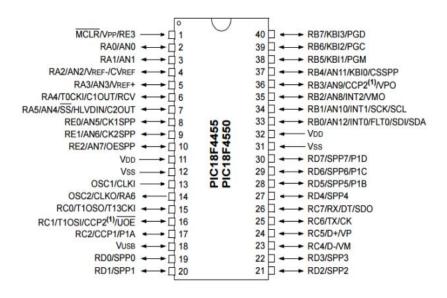

Figura 4 - Pinagem do PIC 18F4550

#### 40-Pin PDIP

Fonte: Microchip Technology (2009)

A descrição detalhada de cada pino se encontra no Quadro 1. A maioria dos pinos possuem mais de uma função, cabendo ao projetista configurar qual utilizar.

Quadro 1 - Descrição dos pinos do PIC18F4550

| Pino | Nome             | Tipo               | Função                                                        |

|------|------------------|--------------------|---------------------------------------------------------------|

| 1    | MCLR/VPP         | In-In              | Reset externo e programação CSP                               |

| 2    | RA0/AN0          | I/O e Input<br>A/D | I/O digital e entrada AD0                                     |

| 3    | RA1/AN1          | I/O e Input<br>A/D | I/O digital e entrada AD1                                     |

| 4    | RA2/AN2/Vref-    | I/O e Input<br>A/D | I/O digital e entrada AD2                                     |

| 5    | RA3/AN3/Vref+    | I/O e Input<br>A/D | I/O digital e entrada AD3 e referência alta do A/D            |

| 6    | RA4/TOCKI        | I/O e Input<br>A/D | I/O digital e entrada TMR0                                    |

| 7    | RA5/AN4/SS/LVDIN | I/O e Inputs       | I/O digital, entrada do A/D4, entrada do SPI e Detector de LV |

| 8    | RE0/RD/AN5       | Fonte              | I/O digital, Leitura da Porta Paralela e entrada do AD5       |

| 9    | RE1/WR/AN6       | Fonte              | I/O digital, Escrita da Porta Paralela e entrada do AD6       |

| 10   | RE2/CS/AN7       | Fonte              | I/O digital, Seleção da Porta Paralela e entrada AD7          |

| 11   | VCC              | Fonte              | Positivo da Fonte de Alimentação                              |

| 12 | GND             | Fonte        | Negativo da Fonte de Alimentação                                |

|----|-----------------|--------------|-----------------------------------------------------------------|

| 13 | OSC1/CLK1       | Input        | Entrada do Crital e entrada do Clock Externo                    |

| 14 | OSC2/CLK2/RA6   | I/O e Inputs | I/O digital, Saída do Cristal e saída do Clock Externo          |

| 15 | RC0/T10S0/T1CK1 | I/O Out e In | I/O digital, saída do 2 oscilador e entrada do contador externo |

|    |                 |              | Timer1/Timer3                                                   |

| 16 | RC1/T10S1/CCP2  | I/O In e Out | I/O digital, saída do 2 oscilador e saída do Módulo CCP2        |

| 17 | RC2/CCP1        | I/O e Out    | I/O digital e saída do Módulo CCP1                              |

| 18 | RC3/SCK/SCL     | I/O, I/O e   | I/O digital, in/out do Clock serial para modo SPI e in/out do   |

| .0 | 1100/0011002    | I/O          | Clock serial para modo I2C                                      |

| 19 | RD0/PSP0        | I/O e I/O    | I/O digital e Porta de Comunicação Paralela                     |

| 20 | RD1/PSP1        | I/O e I/O    | I/O digital e Porta de Comunicação Paralela                     |

| 21 | RD2/PSP2        | I/O e I/O    | I/O digital e Porta de Comunicação Paralela                     |

| 22 | RD3/PSP3        | I/O e I/O    | I/O digital e Porta de Comunicação Paralela                     |

| 23 | RC4/SDI/SDA     | I/O e I/O    | I/O digital e Porta de Comunicação Paralela                     |

| 24 | RC5/SD0         | I/O e I/O    | I/O digital e Saída de Dados SP1                                |

| 25 | RC6/TX/CK       | I/O e I/O    | I/O digital, Transmissão UART e Clock de sincronismo UART       |

| 26 | RC7/RX/DT       | I/O e I/O    | I/O digital, Recepção UART e Dados do UART                      |

| 27 | RD4/PS4         | I/O e I/O    | I/O digital e Porta de Comunicação Paralela                     |

| 28 | RD5/PS5         | I/O e I/O    | I/O digital e Porta de Comunicação Paralela                     |

| 29 | RD6/PS6         | I/O e I/O    | I/O digital e Porta de Comunicação Paralela                     |

| 30 | RD7/PS7         | I/O e I/O    | I/O digital e Porta de Comunicação Paralela                     |

| 31 | GND             | Fonte        | Negativo da Fonte de Alimentação                                |

| 32 | VCC             | Fonte        | Positivo da Fonte de Alimentação                                |

| 33 | RD0/INT0        | I/O e In     | I/O digital e entrada de Interrupção Externa 0                  |

| 34 | RD0/INT1        | I/O e In     | I/O digital e entrada de Interrupção Externa 1                  |

| 35 | RD0/INT2        | I/O e In     | I/O digital e entrada de Interrupção Externa 2                  |

| 36 | RB3/CCP2        | I/O e I/O    | I/O digital Módulo CCP2                                         |

| 37 | RB4             | I/O e In     | I/O digital e entrada de Interrupção por Mudança de Estado      |

| 20 | DDE/DOM         | 1/O o lo     | I/O digital, Interrupção por Mudança de Estado e Habilita       |

| 38 | RB5/PGM         | I/O e In     | ICSP baixa tensão                                               |

| 20 | RB6/PGC I/O     | I/O e In     | I/O digital, Interrupção por Mudança de Estado e ICSP in-       |

| 39 |                 |              | circuit Debuger                                                 |

| 40 | RB7/PGD         | I/O e In     | I/O digital, Interrupção por Mudança de Estado e ICSP in-       |

| 70 |                 |              | circuit Debuger                                                 |

Fonte: Microchip Technology (2009)

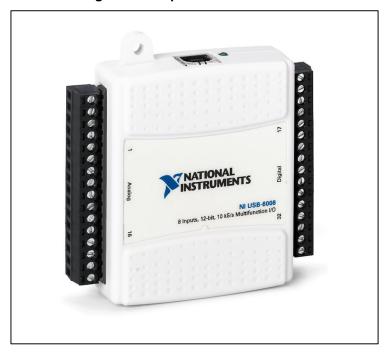

# 3.3 Placa *DAQ* NI-6008

Para o processo de identificação do modelo em espaço de estados do *kit* servomecanismo utiliza-se a placa NI-6008 desenvolvida pela empresa *National Instruments*, ilustrada na Figura 5. Trata-se de um dispositivo multifuncional de baixo custo que oferece funções básicas de aquisição de dados (*Data Acquisition - DAQ*) para aplicações simples de medições portáteis e experimentos de laboratórios acadêmicos.

Figura 5 - Dispositivo DAQ NI-6008

Fonte: National Instruments (2017)

A placa é alimentada por cabo USB, possui 12 entradas/saídas digitais, 2 saídas analógicas (150 Hz), 8 entradas analógicas e um contador de 32 bits. Podese conectar facilmente sensores e sinais através de terminais de parafuso. Possui software que simplifica a configuração e medições, além de possuir fácil integração com MATLAB. Como os demais materiais utilizados neste trabalho, encontra-se disponível na universidade.

#### 3.4 Plataforma MATLAB

MATLAB é uma ferramenta computacional utilizada no auxílio de resolução de problemas científicos e da engenharia. Possui suporte para processamento de sinais, processamento de imagens, robótica, aprendizado de máquina, construção de sistemas de controle, entre outros (MATHWORKS).

No presente trabalho, utiliza-se a plataforma na geração do modelo em espaço de estados do sistema do *kit* servomecanismo, através de um procedimento numérico de identificação. É ainda utilizada na resolução e simulação de resultados dos problemas de otimização convexa gerados a partir das abordagens de *LMIs* descritas no Capítulo 4.

# 3.4.1 Identificação do Modelo Matemático do Kit Servomecanismo

O modelo em espaço de estados do sistema foi construído a partir da resposta a um sinal pseudo aleatório gerado pelo próprio MATLAB e enviado ao motor através da placa DAQ de aquisição de dados. O sinal em questão trabalha diferentes níveis de amplitude e frequência às variáveis de estado de forma a garantir que o modelo gerado represente o sistema com certa precisão para diferentes pontos de operação. O procedimento é descrito a seguir.

Inicialmente monta-se o circuito descrito na Figura 6.

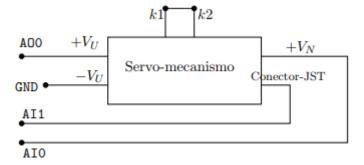

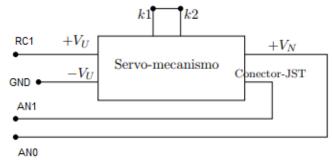

Figura 6 – Circuito para identificação do sistema do servomecanismo

Fonte: Roteiro de experimento "Identificação em espaço de estados e projeto de controle de realimentação completa de estados com rastreamento" (UTFPR, 2017)

No esquemático apresentado, AO0, AI0, AI1 e GND são os terminais da placa DAQ. AO0 é responsável por enviar a tensão gerada pelo sinal pseudo aleatório ao terminal  $V_u$  de entrada do motor. AIO e AI1 coletam os valores de tensão da velocidade angular e corrente JST (Conectores  $V_n$  e JST respectivamente). A tensão em  $V_n$  é diretamente proporcional à velocidade de rotação do motor, ou seja, uma tensão  $V_n$  de 1V equivale a uma velocidade de rotação de 1 radiano por segundo, de acordo com o manual fornecido pela fabricante. Dessa forma o cálculo dos ganhos serão realizados com base nos valores medidos, sem necessidade de condicionamento de sinal.

Uma vez aplicado o sinal pseudo aleatório, armazenam-se os dados de tensão  $V_n$  e de tensão no conector JST nos vetores "vecY" e "vecI" respectivamente, como expresso nos trechos de código a seguir.

```

t1 = tic;

...

for k = 1:numeroAmostras

tensaoMedida = getsample(ai);

vecY = [vecY tensaoMedida(1)];

vecI = [vecI tensaoMedida(2)];

...

end

samprate = (numeroAmostras)/toc % average sampling rate

...

Ts = 1/samprate; %tempo de amostragem

```

Os vetores, juntamente com o tempo de amostragem e a tensão de referência fornecida como estímulo (sinal pseudo aleatório) são os parâmetros utilizados pelo comando *ssest* do MATLAB, que é responsável pela estimativa do modelo em espaço de estados do sistema, como segue:

```

x1real = vecY;

x2real = vecI;

t = [0:Ts:Ts*numeroAmostras];

data = iddata([x1real ; x2real]',vecRef',Ts);

```

```

data.InputName = {'entrada'};

data.OutputName = {'veloc','corrente'};

[modeloIni, x0] = ssest(data,2,'Ts',Ts);

A = modeloIni.A;

B = modeloIni.B;

...

Ac1 = Ts^-1 * (modelo.A - eye(size(modelo.A)))

Bc1 = Ts^-1 * modelo.B

sysc = ss(Ac1,Bc1,modelo.C,0);

figure(1)

compare(data, sysc)

```

O retorno da função *ssest* são as matrizes *A* e *B* estimadas. Como essas matrizes são calculadas considerando um sistema discretizado, realiza-se a multiplicação de ambas por um fator de correção em função do tempo de amostragem, para obter as matrizes de um sistema em tempo contínuo. O modelo é registrado na variável "sysc" e através do comando *compare*, gera-se um gráfico comparativo da resposta do *kit* do servomotor gravada anteriormente e a resposta simulada do sistema estimado para o mesmo sinal pseudo aleatório (vide Resultados e Discussões). O código utilizado na identificação pode ser conferido na íntegra no Anexo I.

Após a modelagem matemática do sistema, constrói-se o problema de otimização via *LMIs* para geração dos ganhos da técnica de controle desenvolvida.

# 3.4.2 Construção e Resolução das *LMIs*

Disponíveis online de forma gratuita, as bibliotecas YALMIP (LÖFBERG, 2012) e ROLMIP (AGULHARI; OLIVEIRA; PERES, 2012) são utilizadas na construção das *LMIs*, bem como na montagem do problema de otimização. A resolução do problema é feita através do *solver* SeDuMi (PÓLIK; ROMANKO; STURM, 2003), também disponível gratuitamente na internet.

As bibliotecas, em conjunto com o solver, tornam a elaboração do problema simples, intuitiva, e permitem o teste de factibilidade. Os resultados encontrados se caracterizam como os ganhos dos controladores para realimentação de estados, e do ganho integrativo.

A seguir um exemplo meramente ilustrativo da construção e resolução de um problema utilizando as ferramentas mencionadas:

```

M = sdpvar(numero_linhas, numero_colunas, 'full');

N = sdpvar(numero_linhas, numero_colunas, 'sym');

a = sdpvar(1,1);

```

No trecho de código, a função sdpvar cria variáveis simbólicas para o problema. O argumento da função recebe o número de linhas e colunas da matriz a ser criada, bem como o seu tipo. No exemplo, a matriz M é uma matriz não simétrica de dimensões  $n \times n$  ou  $n \times m$ , enquanto que a matriz N é uma matriz simétrica de dimensões  $n \times n$ . Para a criação de um valor escalar, basta fornecer o valor 1 para o número de linhas e colunas e omitir o argumento referente ao tipo, como é o caso da variável a.

A estruturação das *LMIs* pode ser feita da seguinte maneira:

```

LMIs = [-M N'; N -V] <= 0;

LMIs = [LMIs, [-a f'; f -X] <= 0];

```

Na primeira linha, a variável *LMIs* recebe a primeira desigualdade. Novas desigualdades podem ser concatenadas com as já existentes, como é o caso da segunda linha. Esse procedimento pode ser realizado até que todas as desigualdes do problema estejam gravadas na variável trabalhada.

A resolução do problema ocorre por meio da função solvesdp:

```

solvesdp(LMIs, funcaoObjetivo,...

sdpsettings('solver','sedumi'));

```

Essa função recebe como argumento o conjunto de *LMIs*, a função a ser minimizada, e as configurações da função (como expresso no exemplo, deve ser feita a seleção do solver).

O teste de factibilidade é realizado através do comando *checkset*:

```

[primal,dual] = checkset(LMIs)

```

Essa função retorna os resíduos de restrição das *LMIs*. Idealmente se a variável "primal" retornada for positiva, ou um número negativo infinitesimal (da ordem de  $10^{-6}$ ), as *LMIs* compõe um problema factível.

O código para construção do problema de otimização via *LMIs* encontra-se no Anexo II.

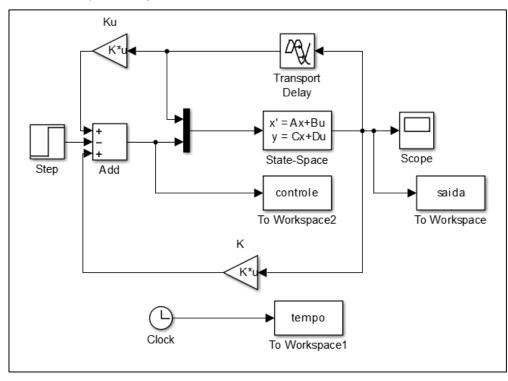

# 3.4.3 Simulação dos controladores via Simulink

Para simulação de desempenho dos controladores gerados a partir da síntese desenvolvida utiliza-se a ferramenta *Simulink*, que é integrada ao MATLAB. Tal ferramenta permite a modelagem, simulação e análise de sistemas dinâmicos, através de um modelo de diagramação gráfica por blocos. Dentre os blocos disponíveis existem modelos prontos para espaço de estados, bem como modelos que geram atraso na transmissão de variáveis, tornando a ferramenta ideal para testes das técnicas de controle tratadas.

# 3.5 Funcionamento do Projeto Embarcado

Já tendo identificado o sistema servomecanismo e calculado os ganhos correspondentes através da síntese de controladores proposta (vide subseção 4.2) e das bibliotecas mencionadas (vide subseção 3.4.2), basta agora o projeto embarcado efetivar a implementação da malha fechada. Ou seja, fazer com que

uma referência seja sempre seguida pelo servomotor, independentemente da existência dos atrasos temporais nas dinâmicas dos estados e na saída de controle.

O PIC18F4550, portanto, controla a velocidade do servomotor através da lei de controle gerada pela relação entre os ganhos previamente calculados e os valores de tensão proporcionais à velocidade angular e corrente JST (conectores  $V_n$  e JST do servomecanismo, respectivamente), ambos lidos constantemente pelos canais AN0 e AN1 do PIC. O microcontrolador, sendo assim, faz as conversões A/D necessárias, desenvolve a saída de controle e a emite em um sinal PWM equivalente no canal RC1 associado ao periférico CCP2. Além dos periféricos já supracitados, a saída serial RS-232C também é utilizada para transmissão dos dados, para análises e validações posteriores. O esquemático geral de funcionamento e da montagem do circuito é dado pelas Figuras 7 e 8.

Servomotor

Velocidade

Conversor A/D

Conversor A/D

Comunicação

Serial

PIC 18F4550

Computador

Figura 7 - Esquemático de funcionamento

Fonte: Autoria Própria

Figura 8 – Esquemático do circuito

Fonte: Autoria Própria

### 3.5.1 Estruturação do Atraso Temporal

A implementação de atrasos temporais conhecidos no sistema é construída a partir de uma estrutura capaz de armazenar uma quantidade finita de dados das variáveis de estado, por um intervalo de tempo que será correspondente ao atraso. Isso é compreendido observando que a síntese desenvolvida para o controlador proposto utiliza também dos valores anteriores ao valor atual para gerar a sua saída de controle. Mais especificamente, o controlador usará constantemente x(t) e x(t-d) para a sua atuação.

Por conseguinte, implementou-se dois vetores, ambos delimitados em duzentas posições de memória, que armazenam os valores atuais e os cento e noventa e nove valores anteriores de tensão dos dois estados do sistema. A delimitação em até duzentas posições foi estabelecida devido a indisponibilidade de espaço na memória do PIC18F4550.

Tais vetores são tratados a partir do conceito de pilhas. Ou seja, os valores lidos pelo microcontrolador são ciclicamente empilhados nas posições de memória dos vetores. Portanto, ao preencher as últimas posições de memória desses vetores tem-se que esses são os valores mais atuais das variáveis de estado do sistema, isto é, x(t). E, a primeira posição que fora preenchida, é o valor anterior mais antigo que se possui registro. Ou seja, x(t-d). Cabe novamente ressaltar que esse processo de alocação é cíclico, logo, quando a última posição de memória é preenchida, o firmware desenvolvido direciona o próximo valor a ser alocado para a primeira posição de memória. Com isso, a segunda posição de memória passa ser o valor anterior mais antigo registrado. Denominando o valor atual como topo da pilha e o valor anterior mais antigo como base, o esquemático a seguir ilustra o conceito apresentado:

topo ÷ ÷ ÷ ŧ base topo (b) (a)

Figura 9 - Esquemático do vetor pilha

Fonte: Autoria Própria

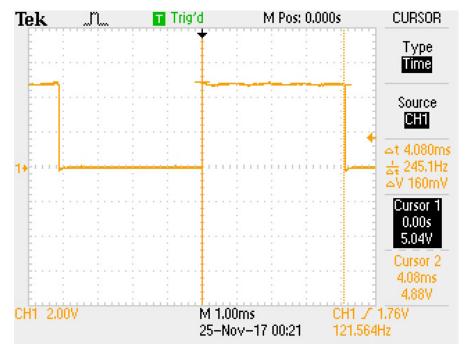

Suprida tal necessidade de projeto, consequentemente, os atrasos temporais surgem pela próprio requerimento de processamento da estrutura criada, pois a criação e a atualização ininterrupta de tais vetores-pilha, somados a todas as outras linhas de código pertencentes ao ciclo 'while' do firmware, possuem um tempo de processamento específico e mensurável. Logo, entendeu-se que o atraso temporal a ser considerado é esse tempo multiplicado pelo número de posições definidas para os vetores, já que pretende-se considerar o maior intervalo de tempo possível que pode ser delimitado pela abordagem apresentada. Nesse sentido, configurou-se um canal auxiliar, o canal RB1, para que ele inverta o seu valor de saída toda vez que o ciclo 'while' reinicie. Tal canal, previamente definido como uma saída digital, foi acoplado ao osciloscópio para conferir o tempo de um ciclo 'while' com precisão. O resultado é ilustrado a seguir:

Figura 10 - Valores de RB1 medidos pelo Osciloscópio

Fonte: Autoria própria

Como foi possível constatar, um ciclo 'while' tem 4,08 milissegundos de duração. Portanto, o atraso temporal estabelecido é de 0,816 segundos. Em suma, é possível verificar o escopo das linhas de código desenvolvidas no firmware do projeto embarcado para implementação das estruturas apresentadas no Anexo III.

#### 3.5.2 Aquisição de dados

Apesar do PIC em uso possuir diversos canais analógicos, só existe um único sistema de conversão. Por isso, é necessário respeitar o tempo de digitalização de cada amostra lida pelo canal analógico em uso, antes que se proceda para uma próxima leitura (seja novamente nesse mesmo canal ou em um outro). Posta a necessidade, é sabido que o tempo de digitalização das amostras é definido a partir de valores para o clock de conversão (TAD) e tempo de aquisição (TACQ), indicados no registrador ADCON2. O trecho de código a seguir representa o processo de configuração e consequente conversão A/D utilizado para o projeto embarcado.

```

ADCON1 = 0b00001101; // Habilita ANO e AN1, Vref+=Vcc e

//Vref-=Vss

ADCON2 = 0b10010101; // Resultado alinhado à direita,

// TACQ = 4TAD e TAD = FOSC/16

while(1) // Loop infinito

{

ADCONO = Ob00000001; // Seleciona ANO

ADCON2 = 0b10010101; // Resultado alinhado à

// direita,

ADCONObits.GO DONE = 1; // Inicia a conversão

// A/D

while (ADCONObits.GO DONE);

Valor conversor = 256 * ADRESH + ADRESL;

// V 1bit = ( Vref+ - Vref-)/(2^10 -1) =

//4,887585 mV

// V sinal analógico = V 1bit *

Valor conversor

. . .

}

```

#### 3.5.3 Geração da Saída de Controle

A lei de controle é calculada utilizando as expressões apresentadas no início deste Capítulo e do termo de ação integral apresentado no Capítulo 2. O desenvolvimento da lei de controle pode ser conferido em mais detalhes no Capítulo 4. Os termos são relembrados a seguir:

$$u(t) = kx(t)$$

,  $u(t-d) = K_u x(t-d)$  e  $I = K_i \int_0^t e(\tau) d\tau$

Após o cálculo da lei de controle pelo firmware, o módulo CCP gera, como saída digital no canal RC1, uma onda quadrada definida pela sua frequência e seu

ciclo de trabalho (do inglês *duty cycle*): o sinal PWM. É possível verificar, a seguir, o trecho de código responsável pela formulação da solução proposta:

```

// Configuração TIMER2

// T = 1/FPWM = 1/10KHz = 100us

// PR2 = {T / [4 * TOSC * (Prescaler do TMR2)]} - 1

// Prescaler do TMR2 = 16

// TOSC = 1/FOSC = 1/20MHz = 50ns

// PR2 = 100us / (4 * 50ns * 16) - 1 = 30,25 = ~31

// BIT 7 = 0 -> Não implementado

// Bit 6-3 = 0000 -> Postscale 1:1

// Bit 2 = 1 -> Timer2 ligado

// Bit 1,0 = 11 -> Prescaler 16.

T2CON = 0b00000111;

CCPR2L = 0b00000000;

CCP2CON = 0b00011100; //inicia com velocidade zerada

while(1) // Loop infinito

//Calculo de Duty Cycle

dc = ((int)u total)/50; //Normaliza de 0 a 100

if(dc < 7) dc = 7;

if(dc > 100) dc = 100;

TDC = 125*dc/100; //Taxa 10kHz

// Configurar CCP2 modo PWM com Duty Cycle

// calculado

// CCPRxL:CCPxCON<5:4> = 375 us/(50 ns *16) =

// = 468,75 = \sim 469

// CCPRxL:CCPxCON<5:4> = 0b0111010101

// Os 8 bits mais significativos de ficam em CCPR2L

// Os 2 bits menos significativos ficam em

```

```

//CCP2CON<5:4>

b8 = TDC&0b11111111100;

b1 = TDC&0b00000000010;

b0 = TDC&0b0000000001;

//Gera PWM

CCPR2L = b8/4;

CCP2CONbits.DC2B1 = b1/2;

CCP2CONbits.DC2B0 = b0;

CCP2CONbits.CCP2M3 = 1;

CCP2CONbits.CCP2M2 = 1;

CCP2CONbits.CCP2M1 = 0;

CCP2CONbits.CCP2M0 = 0;

```

#### 3.5.4 Transmissão de dados

Para posteriores análises do desempenho da implementação do controlador, será necessário transmitir apenas dados numéricos simples. Mais especificamente, o microcontrolador deverá transmitir a um computador os valores de tensão da lei de controle, velocidade angular e corrente JST. Sendo assim, utilizou-se, para tal, uma comunicação serial assíncrona a partir do módulo EUSART do PIC 18F4550. Sua interface é padronizada pela RS-232C.

A configuração necessária é simples, e gira em torno da escolha do *Baud Rate Generator* (*BRG*). Para o projeto em questão, optou-se pelo maior valor possível: 115200. A seguir, um trecho do código desenvolvido para esse aplicação:

```

TXSTAbits.SYNC=0; //Habilita comunicação assíncrona

RCSTAbits.SPEN=1; //Habilita os pinos de I/O para a

//serial

//Configurações transmissor serial

TRISCbits.TRISC6=1; //Habilita o pino TX como entrada

TXSTAbits.TXEN=1

while(1)//loop infinito

{

. . .

while (TXSTAbits.TRMT==0) {}

TXREG=(0x30+(Valor conversor/1000));

while (TXSTAbits.TRMT==0) {}

TXREG=(0x30+((Valor conversor/100)%10));

while (TXSTAbits.TRMT==0) {}

TXREG=(0x30+((Valor conversor/10)%10));

while (TXSTAbits.TRMT==0) {}

TXREG=(0x30+(Valor conversor%10));

while (TXSTAbits.TRMT==0) {}

TXREG=0 \times 0 d;

while (TXSTAbits.TRMT==0) {}

TXREG=0x0a;

. . .

}

```

Por fim, para aquisição dos dados no computador, utilizou-se o software Serial Monitor. Ele basicamente interpreta os bits enviados e disponibiliza os valores numéricos correspondentes em um arquivo de texto padrão.

# **4 RESULTADOS E DISCUSSÕES**

Esse capítulo é dividido em duas partes. Primeiramente, é apresentado o processo de desenvolvimento da técnica de síntese proposta. O modelo baseia-se em uma técnica já apresentada na literatura - vide Yu e Chu (1999) - em que são abordados o controle de um sistema incerto com atrasos em sua dinâmica, otimizando um custo garantido. Como uma extensão dessa síntese, elabora-se um problema de otimização convexa para o caso em que um sistema incerto é afetado por atrasos tanto em sua dinâmica quanto em suas entradas de controle, visando novamente uma solução ótima para o problema do custo garantido (GUEDES; CUNHA; AGULHARI, 2017). O exemplo numérico proposto por Yu e Chu no artigo em que apresentam sua síntese é resolvido, ilustrando o comparativo entre as abordagens propostas.

Em segunda instância, executam-se os passos apresentados acerca da implementação física proposta, como forma de análise de desempenho da síntese desenvolvida, no controle de um sistema real. Os resultados, bem como sua análise, estão aqui documentados.

#### 4.1 Síntese para Sistemas com Atraso nos Estados

Como afirmado anteriormente, essa síntese foi apresentada por Yu e Chu em 1999. Os teoremas são descritos a seguir.

Considere inicialmente o sistema representado pela equação de estados

$$\dot{x}(t) = [A + \Delta A]x(t) + [A_1 + \Delta A_1]x(t - d) + [B + \Delta B]u(t), \tag{19}$$

$$x(t) = \varphi(t), \qquad t \in (-d, 0).$$

Na equação (19), as matrizes A e B representam a dinâmica do sistema e a matriz de entrada, respectivamente. O elemento  $A_1$ , por sua vez, representa a dinâmica atrasada do sistema, enquanto que os termos  $\Delta A$ ,  $\Delta A_1$  e  $\Delta B$  são incertezas limitadas em norma presentes no modelo do sistema. Os vetores x(t), u(t) e  $\varphi(t)$  correspondem, respectivamente, ao vetor de estados, ao vetor de entradas de controle e à função vetorial que caracteriza as condições iniciais do sistema. Por fim, a constante d>0 representa o atraso temporal constante que afeta o sistema.

As incertezas paramétricas consideradas são definidas como

$$[\Delta A \ \Delta B \ \Delta A_1] = DF(t)[E_1 \ E_2 \ E_d], \tag{20}$$

sendo D,  $E_1$ ,  $E_2$  e  $E_d$  matrizes constantes reais que representam as estruturas das incertezas. A função F(t) uma função matricial desconhecida com elementos mensuráveis, que satisfaz  $F'(t)F(t) \leq I$ , em que I é a matriz identidade de dimensões apropriadas.

Associado ao sistema (19), tem-se a função de custo (14), apresentada no Capítulo 2 e reproduzida a seguir,

$$J = \int_0^\infty [x'(t)Qx(t) + u'(t)Ru(t)]dt.$$

O principal objetivo do método apresentado por Yu e Chu (1999) é computar uma lei de controle u(t), que garanta a estabilidade do sistema afetado pelas incertezas e pelo atraso, minimizando também o custo J. Tal método é brevemente apresentado nos Teoremas 1, 2 e 3.

**Teorema 1:** O controlador u(t) = Kx(t) estabiliza o sistema (19) e satisfaz o custo garantido J se existirem matrizes simétricas positivas-definidas  $P, S \in \mathbb{R}^{nxn}$  tais que, para toda matriz de incertezas F(t) satisfazendo a condição  $F'(t)F(t) \leq I$ ,

$$\begin{bmatrix} \Sigma & P(A_1 + DF(t)E_d) \\ (A_1 + DF(t)E_d)'P & -S \end{bmatrix} < 0, \tag{21}$$

sendo

$$\Sigma = Q + K'RK + S + P[A + BK + DF(t)(E_1 + E_2K)] +$$

$$+ [A + BK + DF(t)(E_1 + E_2K)]'P.$$

(21.1)

**Teorema 2:** Para o sistema (19), existem matrizes simétricas positivas-definidas P, S tais que a desigualdade matricial (21) é verdadeira se, e somente se, existir um escalar  $\varepsilon > 0$ , uma matriz  $W \in R^{mxn}$  e matrizes simétricas positivas-definidas  $X, V \in R^{nxn}$  tais que a condição a seguir é satisfeita

$$\begin{bmatrix} \tilde{A} & A_1 V & (E_1 X + E_2 W)' & X & W & X \\ V A_1' & -V & V E_d' & 0 & 0 & 0 \\ E_1 X + E_2 W & E_d V & -\varepsilon I & 0 & 0 & 0 \\ X & 0 & 0 & -Q^{-1} & 0 & 0 \\ W & 0 & 0 & 0 & -R^{-1} & 0 \\ X & 0 & 0 & 0 & 0 & -V \end{bmatrix} < 0, \tag{22}$$

sendo  $\tilde{A}=(AX+BW)+(AX+BW)'+\varepsilon DD', \ X=P^{-1}, \ W=KP^{-1}$  e  $V=S^{-1}$ . A mudança de variáves de K, P e S é feita para que se mantenha a convexidade da condição. Se a equação (22) possuir soluções factíveis  $\varepsilon,W,X>0,V>0$ , então a lei de controle por realimentação de estados

$$u^*(t) = WX^{-1}x(t), (23)$$

em que  $K = WX^{-1}$ , é uma lei de controle que garante um custo

$$J \le J^* = \varphi'(0)X^{-1}\varphi(0) \int_{-d}^0 \varphi'(\tau)V^{-1}\varphi(\tau)d\tau \tag{24}$$

para o sistema incerto (19).

**Teorema 3:** O sistema (19) com função de custo (14) possui lei de controle (23) que garante a estabilidade e custo reduzido se existirem soluções factíveis  $\varepsilon$ ,  $\alpha$ , W, X, V e M para o problema de otimização:

$$\min_{\varepsilon, \alpha, W, V, M} \alpha + tr(M), \tag{25}$$

sujeito a

(i)(22);

$$(ii)\begin{bmatrix} -\alpha & \varphi'(0) \\ \varphi(0) & -X \end{bmatrix} < 0;$$

$$(iii)\begin{bmatrix} -M & N' \\ N & -V \end{bmatrix} < 0;$$

em que  $\int_{-d}^{0} \varphi'(\tau) \varphi(\tau) d\tau = NN'$ .

As demonstrações dos Teoremas apresentados podem ser conferidas com detalhes em Yu e Chu (1999). É importante detalhar que as demonstrações são baseadas na utilização da função de Lyapunov

$$V(x) = x'(t)Px(t) + \int_{t-d}^{t} x'(\tau)Sx(\tau)d\tau,$$

(26)

composta de um termo quadrático e da integral do atraso que afeta o sistema.

Embora o desenvolvimento apresentado nessa subseção não considere atrasos relativos à entrada de controle, essa é uma situação frequentemente

encontrada em sistemas físicos. Na próxima subseção realiza-se a extensão desse caso, a fim de considerar tal situação.

# 4.2 Desenvolvimento de Síntese para Sistemas com Atraso nos Estados e na Entrada de Controle

A seguir, é apresentada a técnica de síntese desenvolvida e previamente publicada pelos autores do presente trabalho no Simpósio Brasileiro de Automação Inteligente (GUEDES; CUNHA; AGULHARI, 2017).

Considere agora um sistema que possui, além do atraso na dinâmica, um atraso na entrada de controle representado pela parcela  $[B_1 + \Delta B_1]u(t-d)$ , como descrito em (27)

$$\dot{x}(t) = [A + \Delta A]x(t) + [A_1 + \Delta A_1]x(t - d) + [B + \Delta B]u(t) + [B_1 + \Delta B_1]u(t - d)$$

$$x(t) = \varphi(t), \ t \in (-d, 0), \tag{27}$$

Associado também ao sistema (27), tem-se a função de custo (14). As incertezas paramétricas consideradas são dadas por

$$[\Delta A \ \Delta B \ \Delta A_1 \ \Delta B_1] = DF(t)[E_1 \ E_2 \ E_d \ E_u]. \tag{28}$$

O equivalente ao Teorema 1 para o sistema (27) é dado pelo Teorema 4.

**Teorema 4:** Os controladores u(t) = Kx(t) e  $u(t-d) = K_ux(t-d)$  satisfazem o custo garantido se existirem matrizes simétricas positivas-definidas  $P, S \in R^{nxn}$  tais que, para toda matriz de incertezas F(t) satisfazendo a condição  $F'(t)F(t) \leq I$ ,

$$\begin{bmatrix}

\Sigma & P[A_1 + B_1 K_u + DF(t)(E_d + K_u E_u)]'P & P[A_1 + B_1 K_u + DF(t)(E_d + K_u E_u)] \\

-S

\end{bmatrix} < 0,$$

(29)

sendo

$$\Sigma = Q + K'RK + S + P[A + BK + DF(t)(E_1 + E_2K)] +$$

$$+ [A + BK + DF(t)(E_1 + E_2K)]'P.$$

(29.1)

**Prova.** Considere u(t) = Kx(t) e  $u(t-d) = K_ux(t-d)$ . A representação em malha fechada do sistema (27) é dada por

$$\dot{x}(t) = [A + BK + DF(t)(E_1 + E_2K)]x(t) +$$

$$+ [A_1 + B_1K_u + DF(t)(E_d + E_uK_u)]x(t - d).$$

(30)

O resultado da derivada em relação ao tempo da Função de Lyapunov (26) ao longo de qualquer trajetória do sistema de malha fechada (30) é

$$\dot{V}(x) = \dot{x}'(t)Px(t) + x'(t)P\dot{x}(t) + x'(t)Sx(t) - x'(t-d)Sx(t-d)$$

(31.1)

$$\dot{V}(x) = x'(t)[A + BK + DF(t)(E_1 + E_2K)]'Px(t) +$$

$$+x'(t)P[A + BK + DF(t)(E_1 + E_2K)]x(t) +$$

$$+x'(t - d)[A_1 + B_1K_u + DF(t)(E_d + E_uK_u)]'Px(t) +$$

$$+x'(t)P[A_1 + B_1K_u + DF(t)(E_d + E_uK_u)]x(t - d) +$$

$$+x'(t)Sx(t) - x'(t - d)Sx(t - d)$$

(31.2)

$$\dot{V}(x) = \begin{bmatrix} x(t) \\ x(t-d) \end{bmatrix}' \begin{bmatrix} \phi \\ [A_1 + B_1 K_u + DF(t)(E_d + E_u K_u)]'P \end{bmatrix}$$

$$P[A_1 + B_1 K_u + DF(t)(E_d + E_u K_u)] \begin{bmatrix} x(t) \\ x(t-d) \end{bmatrix}$$

$$< \begin{bmatrix} x(t) \\ x(t-d) \end{bmatrix}' \begin{bmatrix} -Q - K'RK & 0 \\ 0 & 0 \end{bmatrix} \begin{bmatrix} x(t) \\ x(t-d) \end{bmatrix}, \quad (31.3)$$

Sendo  $\phi = S + P[A + BK + DF(t)(E_1 + E_2K)] + [A + BK + DF(t)(E_1 + E_2K)]'P$ . Logo

$$\dot{V}(x) = \begin{bmatrix} x(t) \\ x(t-d) \end{bmatrix}' \begin{bmatrix} \Sigma \\ [A_1 + B_1 K_u + DF(t)(E_d + E_u K_u)]'P \end{bmatrix}$$

$$P[A_1 + B_1 K_u + DF(t)(E_d + E_u K_u)] \begin{bmatrix} x(t) \\ x(t-d) \end{bmatrix} < 0. \quad (31.4)$$

Assumindo a estabilidade assintótica (KHALIL, 2002) do sistema de malha fechada (27), tem-se que  $\dot{V}(x) \leq 0$ . A condição (29) implica

$$\dot{V}(x) < x'(t)(-Q - K'RK)x(t) < 0. \tag{32}$$

Segue da demonstração do Teorema 1 em Yu e Chu (1999) que a integral da equação (32) resulta em

$$\int_0^\infty x'(t)(Q+K'RK)x(t)dt \le \varphi'(0)P\varphi(0) + \int_{-d}^0 \varphi'(\tau)S\varphi(\tau)d\tau.$$

(33)

Assim sendo, u(t) = Kx(t) e  $u(t-d) = K_ux(t-d)$  são controladores com custo garantido se existirem matrizes simétricas positivas-definidas  $P, S \in \mathbb{R}^{n \times n}$  tal que para toda matriz de incertezas F(t) satisfazendo a condição  $F'(t)F(t) \leq I$ , a equação (29) é satisfeita.

O Teorema 5 apresenta uma desigualdade matricial linear cuja solução garante a existência de  $P,S \in \mathbb{R}^{n \times n}$  que satisfaçam a condição (29), responsável também por gerar os ganhos de realimentação de estados K e  $K_u$  que estabilizam o sistema e minimizam um limitante para o custo J.

**Teorema 5:** Para o sistema (27), existem matrizes simétricas positivas-definidas P,S tais que a desigualdade matricial (29) é verdadeira se, e somente se, existirem um escalar  $\varepsilon > 0$ , matrizes  $W,Z \in \mathbb{R}^{mxn}$  e matrizes simétricas positivas-definidas  $X,V \in \mathbb{R}^{nxn}$  tais que a seguinte desigualdade matricial linear é satisfeita.

$$\begin{bmatrix} \tilde{A} & A_{1}V + B_{1}Z & (E_{1}X + E_{2}W)' & X & W & X \\ (A_{1}V + B_{1}Z)' & -V & (E_{d}V + E_{u}Z)' & 0 & 0 & 0 \\ E_{1}X + E_{2}W & E_{d}V + E_{u}Z & -\varepsilon I & 0 & 0 & 0 \\ X & 0 & 0 & -Q^{-1} & 0 & 0 \\ W & 0 & 0 & 0 & -R^{-1} & 0 \\ X & 0 & 0 & 0 & 0 & -V \end{bmatrix} < 0, \quad (34)$$

sendo  $\tilde{A}=(AX+BW)+(AX+BW)'+\varepsilon DD', X=P^{-1}, W=KP^{-1}, V=S^{-1}, e Z=K_uS^{-1}.$  A mudança de variáveis de K,  $K_u$ , P e S é feita para que se mantenha a convexidade da condição. Se a equação (34) possuir soluções factíveis  $\varepsilon$ , W, Z, X>0, V>0, então a lei de controle por realimentação de estados

$$u^{*}(t) = WX^{-1}x(t)$$

$$u^{*}(t-d) = ZV^{-1}x(t-d)$$

(35)

com  $K = WX^{-1}$  e  $K_u = ZV^{-1}$ , é uma lei de controle que garante um custo (14) para o sistema incerto (27).

Prova. Define-se

$$Y = \begin{bmatrix} Q + K'RK + S + P(A + BK) + (A + BK)'P & P(A_1 + B_1K_u) \\ (A_1 + B_1K_u)'P & -S \end{bmatrix}$$

(36)

Logo, a equação (29) equivale a

$$Y + \begin{bmatrix} PD \\ 0 \end{bmatrix} F(t) [E_1 + E_2 K \quad E_d + E_u K_u] + [E_1 + E_2 K \quad E_d + E_u K_u]' F'(t) \begin{bmatrix} PD \\ 0 \end{bmatrix}' < 0.$$

(36.1)

Pelo Lema 2.4 em Xie (1996), a desigualdade acima é satisfeita para todo F(t), tal que  $F'(t)F(t) \le I$  se, e somente se, existir um escalar  $\varepsilon > 0$  de modo que

$$Y + \varepsilon {PD \brack 0} {PD \brack 0}' + \varepsilon^{-1} [E_1 + E_2 K \quad E_d + E_u K_u]' [E_1 + E_2 K \quad E_d + E_u K_u] < 0, \quad (36.2)$$

o que equivale a

$$\left[ (A_1 + B_1 K_u)'P + \varepsilon^{-1} (E_d + E_u K_u)'(E_1 + E_2 K) \right]

P(A_1 + B_1 K_u) + \varepsilon^{-1} (E_1 + E_2 K)'(E_d + E_u K_u)

-S + \varepsilon^{-1} (E_d + E_u K_u)'(E_d + E_u K_u) \right] < 0,$$

(37)

Sendo

$$\Omega = Q + K'RK + S + P(A + BK) + (A + BK)'P +$$

$$+ \varepsilon PDD'P + \varepsilon^{-1}(E_1 + E_2K)'(E_1 + E_2K).$$

(37.1)

Pelo complemento Schur, a equação (37) pode ser reescrita como

$$\begin{bmatrix} \hat{A} & P(A_1 + B_1 K_u) & (E_1 + E_2 K)' & I & K & I \\ (A_1 + B_1 K_u)'P & -S & (E_d + E_u K_u)' & 0 & 0 & 0 \\ (E_1 + E_2 K) & E_d V + E_u Z & -\varepsilon I & 0 & 0 & 0 \\ I & 0 & 0 & -Q^{-1} & 0 & 0 \\ K & 0 & 0 & 0 & -R^{-1} & 0 \\ I & 0 & 0 & 0 & 0 & -S^{-1} \end{bmatrix} < 0, (38)$$

sendo  $\hat{A} = P(A + BK) + (A + BK)'P + \varepsilon PDD'P$ . Multiplicando ambos os lados da equação (38) por

$$\begin{bmatrix} P^{-1} & 0 & 0 & 0 & 0 & 0 \\ 0 & S^{-1} & 0 & 0 & 0 & 0 \\ 0 & 0 & I & 0 & 0 & 0 \\ 0 & 0 & 0 & I & 0 & 0 \\ 0 & 0 & 0 & 0 & I & 0 \\ 0 & 0 & 0 & 0 & 0 & I \end{bmatrix},$$

(39)

e realizando a mudança de variáveis,  $X=P^{-1}$ ,  $W=KP^{-1}$ ,  $V=S^{-1}$ , e  $Z=K_uS^{-1}$ , dadas condições X=X'>0, V=V'>0, obtém-se a equação (34).

Por fim, equivalente à abordagem de Yu e Chu (1999), computar uma lei de controle de custo garantido para o sistema de desigualdades matriciais lineares proposto equivale à resolução de um problema de otimização. Para o sistema (27) tal problema de otimização é dado a seguir.