## UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁ PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA E INFORMÁTICA INDUSTRIAL

MAICON BRUNO HOFMANN

Implementação em FPGA de compensadores de desvios para Conversor Analógico Digital Intercalado

DISSERTAÇÃO

**CURITIBA**

2016

### MAICON BRUNO HOFMANN

## Implementação em FPGA de compensadores de desvios para Conversor Analógico Digital Intercalado

Dissertação apresentada ao Programa de Pósgraduação em Engenharia Elétrica e Informática Industrial da Universidade Tecnológica Federal do Paraná como requisito parcial para obtenção do grau de "Mestre em Ciências" – Área de Concentração: Engenharia de Automação e Sistemas.

Orientador: Prof. Ph.D. André Augusto

Mariano

Co-orientadora: Prof<sup>a</sup>. Dra. Sibilla Batista da Luz França

**CURITIBA**

#### Dados Internacionais de Catalogação na Publicação

Hofmann, Maicon Bruno

H713i 2016 Implementação em FPGA de compensadores de desvios para conversor analógico digital intercalado / Maicon Bruno Hofmann.-- 2016.

98 f.: il.; 30 cm.

Dissertação (Mestrado) - Universidade Tecnológica Federal do Paraná. Programa de Pós-graduação em Engenharia Elétrica e Informática Industrial, Curitiba, 2016

Bibliografia: f. 94-97

1. Conversores analógicos digitais. 2. Arranjos de lógica programável em campo. 3. VHDL (Linguagem descritiva de hardware). 4. Engenharia elétrica - Dissertações. I. Mariano, André Augusto, orient. II. França, Sibilla Batista da Luz, coorient. III. Universidade Tecnológica Federal do Paraná. Programa de Pós-Graduação em Engenharia Elétrica e Informática Industrial. IV. Título.

CDD: Ed. 22 -- 621.3

## UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁ

Programa de Pós-Graduação em Engenharia Elétrica e Informática Industrial

| Título | da | Dissertação Nº. |  |

|--------|----|-----------------|--|

|        |    |                 |  |

## Implementação Em FPGA De Compensadores De Desvios Para Conversor Analógico Digital Intercalado

por

## Maicon Bruno Hofmann

Orientador: Prof. Dr. André Augusto Mariano (*UTFPR*)

Coorientadora: Prof<sup>a</sup>. Dr. Sibilla Batista da Luz França(UFPR)

Esta dissertação foi apresentada como requisito parcial à obtenção do grau de MESTRE EM CIÊNCIAS – Área de Concentração: **Engenharia de Automação e Sistemas** do Programa de Pós-Graduação em Engenharia Elétrica e Informática Industrial – CPGEI – da Universidade Tecnológica Federal do Paraná – UTFPR, às 14 h do dia 15 de março 2016. O trabalho foi aprovado pela Banca Examinadora, composta pelos professores doutores:

Prof. Dr. André Augusto Mariano (Presidente – UTFPR) Prof. Dr. Luis Henrique Assumpção Lolis (UFPR)

Prof. Dr. Glauber Gomes de Oliveira Brante (UTFPR)

Visto da coordenação:

Prof. Dr. Emilio Carlos Gomes Wille (Coordenador do CPGEI) Dedico este trabalho a minha amada Suélin, que esteve ao meu lado desde o início desta jornada, me incentivando, apoiando e comemorando comigo todas as conquistas; mas principalmente por compreender os motivos de minha ausência durante todo este período.

#### **AGRADECIMENTOS**

Primeiramente agradeço a Deus e a minha família.

Agradeço ao meu orientador e co-orientadora, pela paciência e compreensão ao longo destes anos, principalmente nos momentos em que cometi falhas. Sinto-me lisonjeado pela oportunidade que tive de receber seus ensinamentos e orientação.

Agradeço aos professores da UFPR e aos alunos do grupo GICS, pelas valiosas dicas e observações dadas durante as minhas apresentações no grupo. Em especial ao Raphael, pelo tempo que disponibilizou para me ensinar os métodos de teste utilizados pelo Allan; e ao professor Lima, pelas conversas de assuntos aleatórios e companheirismo durante o SBRT.

Agradeço aos membros da banca, professor Glauber Rocha e Luis Lolis, pelas contribuições ao texto final deste trabalho.

Agradeço aos meus professores de graduação na UDESC, Aleksander Paterno e Pedro Bertemes, que me deram o primeiro incentivo para a pesquisa acadêmica.

E por último, mas não menos importante, a minha noiva, pelo incentivo durante todo o desenvolvimento deste trabalho, e por tirar a minha atenção dele de vez em quando.

#### **RESUMO**

HOFMANN, Maicon. Implementação em FPGA de compensadores de desvios para Conversor Analógico Digital Intercalado. 99 f. Dissertação – Programa de Pós-graduação em Engenharia Elétrica e Informática Industrial, Universidade Tecnológica Federal do Paraná. Curitiba, 2016.

Este trabalho apresenta a modelagem e implementação em FPGA de sistemas digitais de compensação de desvios para TIADC (Time Interleaved Analog to Digital Converter). O desenvolvimento de todo este trabalho seguiu uma metodologia top-down. Seguindo esta metodologia foi elaborada a modelagem comportamental de um TIADC de dois canais e seus respectivos desvios de offset, ganho e clock skew em Simulink. A modelagem comportamental de sistemas digitais de compensação para estes desvios também foi realizada seguindo esta metodologia. Para o desvio de clock skew foi utilizada a compensação através de filtros de delay fracionário, mais especificamente, a eficiente estrutura de Farrow. A definição de qual método seria utilizado para o projeto do filtro, e da estrutura de Farrow, exigiu um estudo de diversos métodos de projeto apresentados na literatura. Os sistemas digitais de compensação modelados foram convertidos em código VHDL, para implementação e validação em FPGA. A validação destes sistemas foi realizada utilizando a metodologia de teste FPGA In Loop. Os resultados obtidos com os compensadores de desvio do TIADC demonstram o elevado ganho de desempenho fornecido por estas estruturas. Além deste resultado, este trabalho ilustra o potencial das metodologias de desenvolvimento, implementação e teste em FPGA utilizadas para a obtenção destes compensadores.

**Palavras-chave:** Conversor analógico digital intercalado, Farrow, Clock Skew, FPGA, Modelagem Simulink

#### **ABSTRACT**

HOFMANN, Maicon. FPGA IMPLEMENTATION OF TIME INTERLEAVED ANALOG TO DIGITAL CONVERTER MISMATCHES COMPENSATORS. 99 f. Dissertação – Programa de Pós-graduação em Engenharia Elétrica e Informática Industrial, Universidade Tecnológica Federal do Paraná. Curitiba, 2016.

This work presents the modeling and FPGA implementation of digital TIADC mismatches compensation systems in a top-down methodology. A two channel TIADC and their respective offset, gain and clock skew mismatches behavior modeling was done on Simulink. In addition, was developed digital mismatch compensation system behavior modeling. Fractionaç delay filters were used for clock skew mismatch compensation, more specifically, the efficient Farrow structure. To define the filter design, and Farrow structure design, methodology a study of various design methods present in literature were required. The digital compensation systems models were converted to VHDL, for FPGA implementation and validation. These system validation was carried out using the test methodology FPGA In Loop. The results obtained show the high performance gain provided by these digital systems. Beyond this result, these work illustrates the potential of design, implementation and FPGA test methodologies.

**Keywords:** Time Interleaved ADC, Farrow, Clock Skew, FPGA, Simulink Modeling

## LISTA DE FIGURAS

| FIGURA 1 – Funcão de transferência de um ADC ideal                                           | 20 |

|----------------------------------------------------------------------------------------------|----|

| FIGURA 2 - SFDR                                                                              | 22 |

| FIGURA 3 - TIADC                                                                             | 23 |

| FIGURA 4 – Função de transferência de ADC com <i>offset</i>                                  | 25 |

| FIGURA 5 – Espectro TIADC com offset                                                         | 25 |

| FIGURA 6 – Função de transferência de um ADC com desvio no ganho                             | 26 |

| FIGURA 7 – Espectro TIADC com desvio de ganho                                                | 26 |

| FIGURA 8 – Aperture Delay                                                                    | 27 |

| FIGURA 9 – Espectro do TIADC com <i>clock skew</i>                                           | 28 |

| FIGURA 10 – SNR versus $f_{in}$ de um TIADC com $clock$ $skew$                               | 29 |

| FIGURA 11 – Resposta ao impulso filtro de <i>delay</i> fracionário ideal                     | 36 |

| FIGURA 12 – Magnitude do filtro projetado através do método Least Square                     | 38 |

| FIGURA 13 – Atraso de fase do filtro projetado através do método Least Square                | 38 |

| FIGURA 14 – Magnitude de filtros projetados utilizando método GLS para $\alpha = 0.5 \dots$  | 41 |

| FIGURA 15 – Atraso de fase de filtros projetados utilizando método GLS para $\alpha = 0.5$ . | 41 |

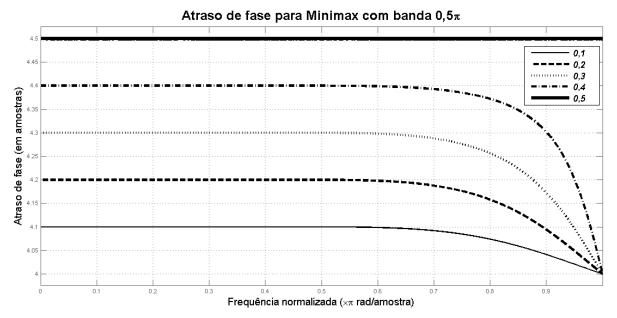

| FIGURA 16 – Magnitude de filtros projetados utilizando método Minimax para banda             |    |

| de $0.5\pi$                                                                                  | 44 |

| FIGURA 17 - Atraso de fase de filtros projetados utilizando método Minimax para              |    |

| banda de $0.5\pi$                                                                            | 44 |

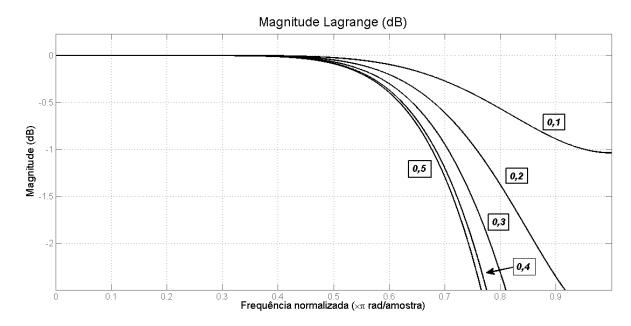

| FIGURA 18 – Magnitude de filtros projetados utilizando Lagrange                              | 45 |

| FIGURA 19 – Atraso de fase de filtros projetados utilizando Lagrange                         | 46 |

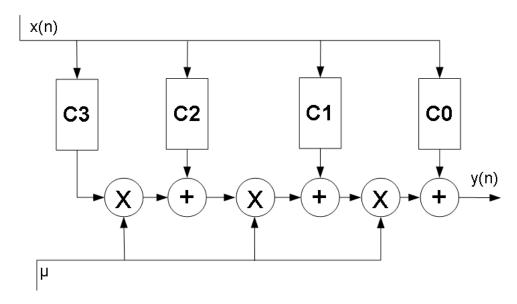

| FIGURA 20 – Estrutura de Farrow                                                              | 48 |

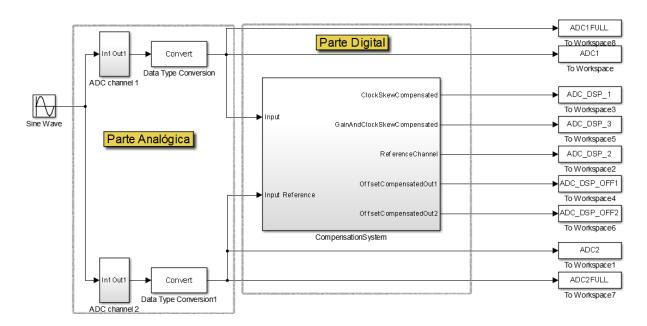

| FIGURA 21 – Visão geral da modelagem do TIADC                                                | 53 |

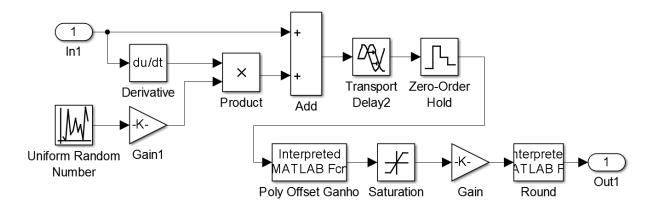

| FIGURA 22 - Modelo interno do ADC                                                            | 54 |

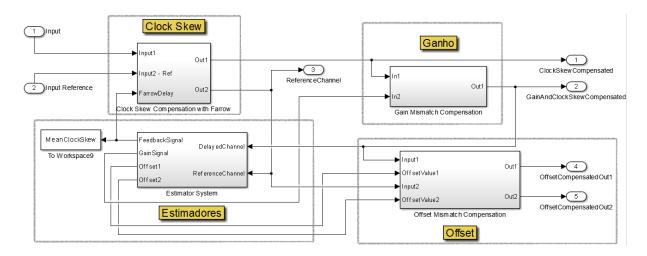

| FIGURA 23 – Estrutura geral dos compensadores de desvio                                      | 55 |

| FIGURA 24 – Modelo teste da ordem do filtro                                                  | 57 |

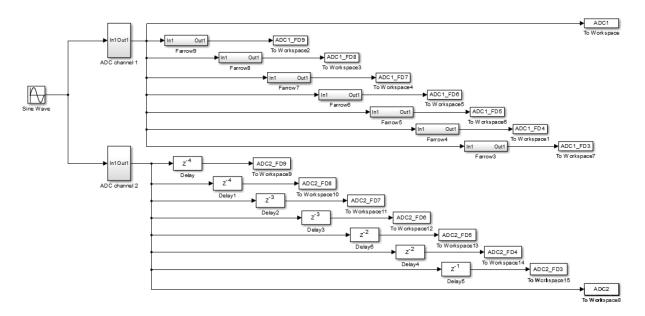

| FIGURA 25 – Modelo de teste da estrutura de Farrow Lagrange                                  | 57 |

| FIGURA 26 – Modelo de comparação dos filtros                                                 | 59 |

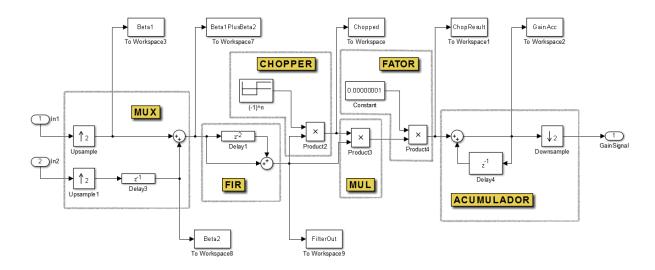

| FIGURA 27 – Modelagem do compensador de <i>clock skew</i> com estrutura de Farrow            | 61 |

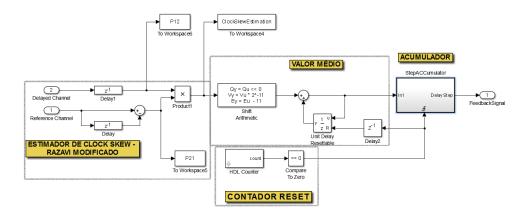

| FIGURA 28 – Modelo do estimador de <i>clock skew</i> proposto por Razavi                     | 62 |

| FIGURA 29 - Modelo do estimador de clock skew proposto por Razavi com                        |    |

| modificações                                                                                 | 63 |

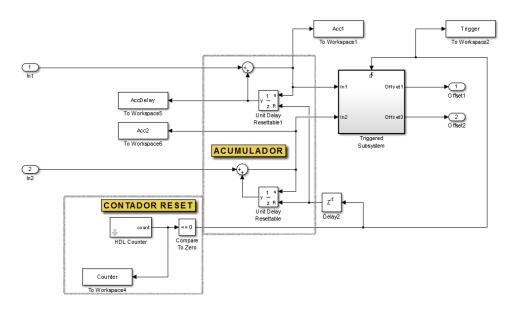

| FIGURA 30 – Modelo do estimador de ganho                                                     | 64 |

| FIGURA 31 – Modelo do estimador de <i>offset</i>                                             | 65 |

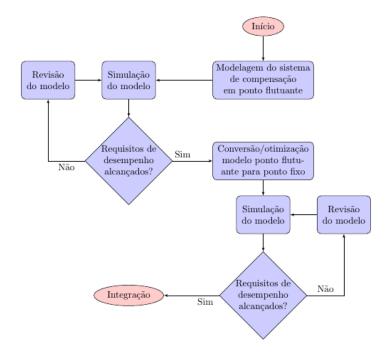

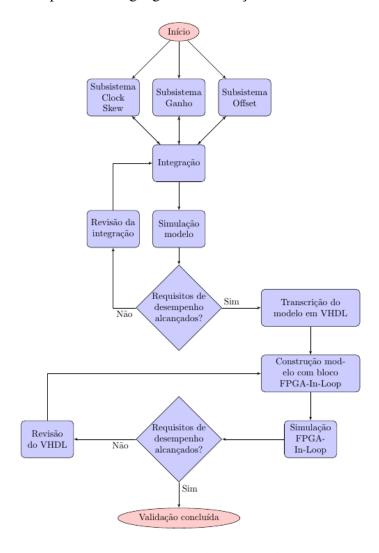

| FIGURA 32 - Fluxograma do processo de desenvolvimento dos subsistemas de                     |    |

| compensação                                                                                  | 67 |

| FIGURA 33 - Fluxograma do processo de desenvolvimento do sistema completo de                 |    |

| compensação                                                                                  | 68 |

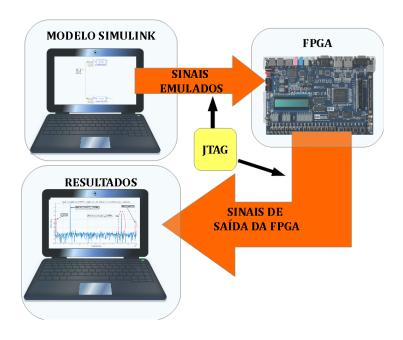

| FIGURA 34 – Ilustração do processo de teste FPGA In Loop                                     | 70 |

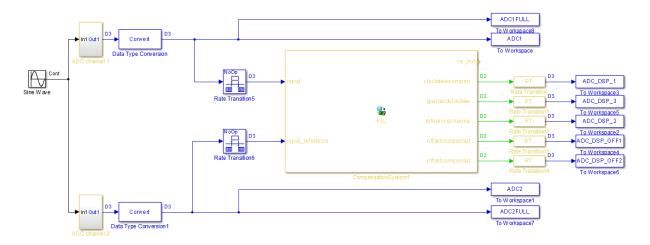

| FIGURA 35 – Diagrama de interface da simulação FPGA In Loop                                  | 71 |

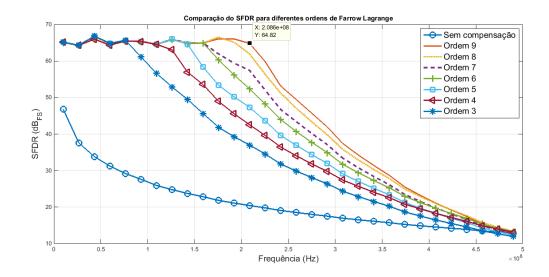

| FIGURA 36 – Gráfico da comparação de ordem da estrutura de Farrow Lagrange                   | 74 |

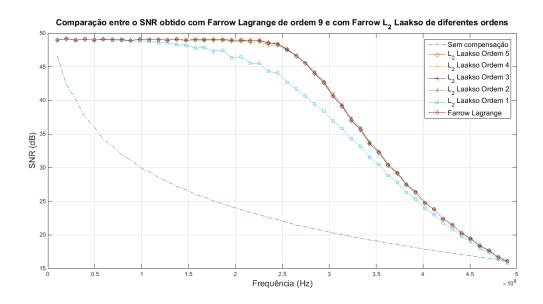

| FIGURA 37 – Gráfico do SNR para comparação da estrutura de Farrow Lagrange com               |    |

|           | L <sub>2</sub> Laakso                                                         | 75 |

|-----------|-------------------------------------------------------------------------------|----|

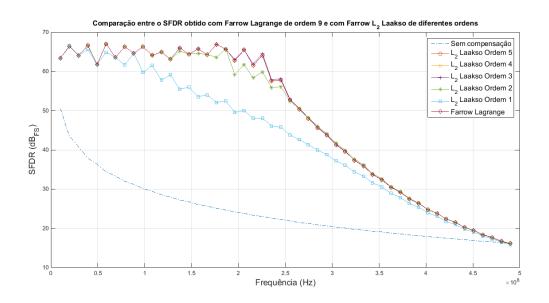

| FIGURA 38 | - Gráfico do SFDR para comparação da estrutura de Farrow Lagrange com         |    |

|           | L <sub>2</sub> Laakso                                                         | 75 |

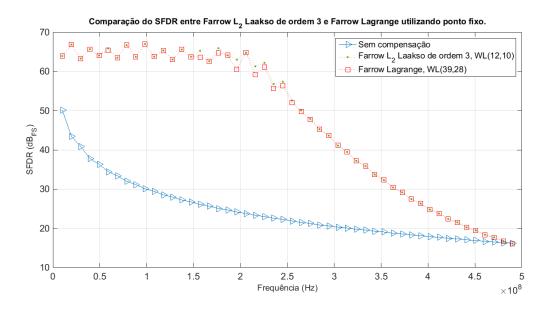

| FIGURA 39 | - Gráfico do SFDR para comparação da estrutura de Farrow Lagrange com         |    |

|           | <i>L</i> <sub>2</sub> Laakso em ponto fixo                                    | 76 |

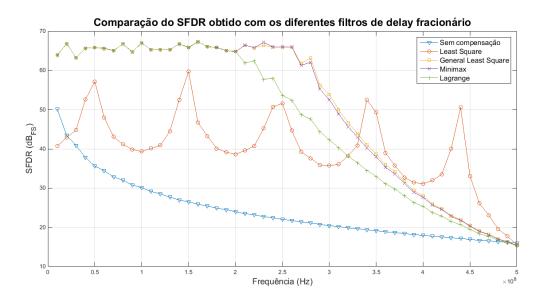

| FIGURA 40 | - Gráfico do SFDR para comparação de diferentes filtros de delay              |    |

|           | fracionário                                                                   | 76 |

| FIGURA 41 | - Gráfico do SFDR para comparação da ordem e da faixa de delay da             |    |

|           | estrutura $L_2$ Laakso com filtro GLS                                         | 77 |

| FIGURA 42 | - Gráfico da magnitude do erro de aproximação da estrutura de Farrow $L_2$    |    |

|           | Laakso com filtro de Lagrange.                                                | 78 |

| FIGURA 43 | - Gráfico da magnitude do erro de aproximação da estrutura de Farrow $L_2$    |    |

|           | Laakso com filtro GLS                                                         | 79 |

| FIGURA 44 | - Curva do valor estimado de <i>delay</i> para compensação do clock skew      | 80 |

| FIGURA 45 | - Espectro do TIADC com <i>clock skew</i> e sem compensação                   | 81 |

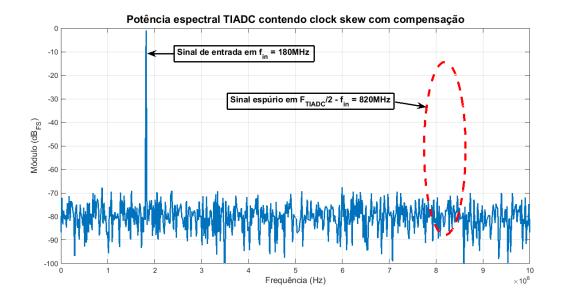

|           | - Espectro do TIADC com <i>clock skew</i> e com compensação                   | 82 |

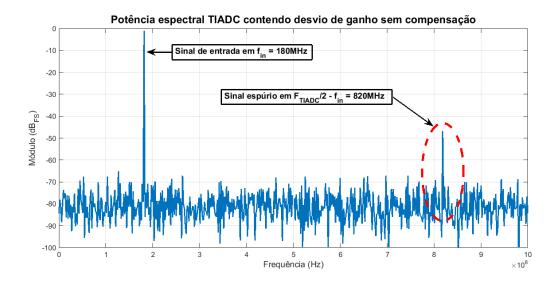

|           | - Espectro TIADC com desvio de ganho e sem compensação                        | 83 |

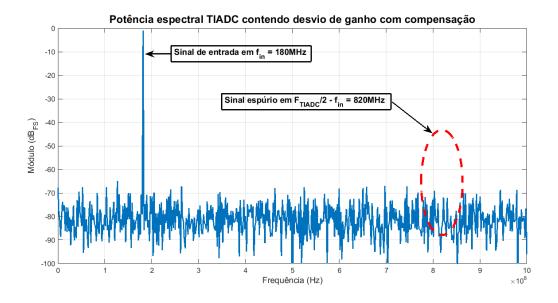

|           | - Espectro TIADC com desvio de ganho e com compensação                        | 83 |

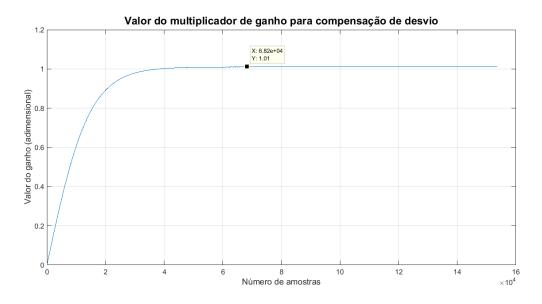

| FIGURA 49 | - Curva do multiplicador de ganho ao longo do tempo                           | 84 |

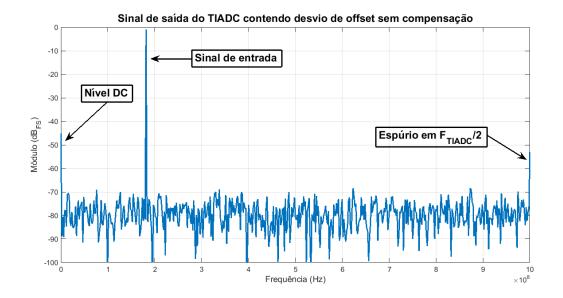

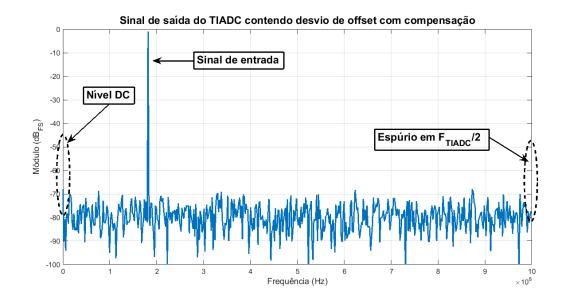

| FIGURA 50 | - Espectro TIADC com desvio de offset e sem compensação                       | 85 |

| FIGURA 51 | - Espectro TIADC com desvio de <i>offset</i> e com compensação                | 86 |

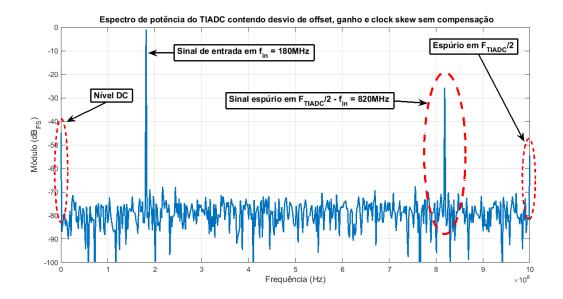

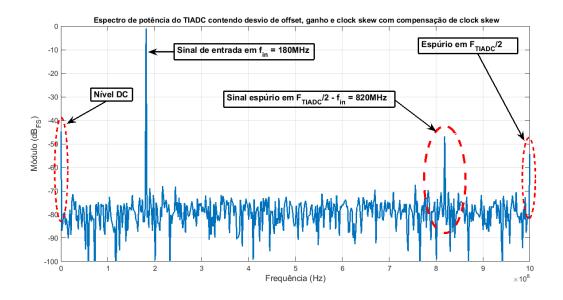

| FIGURA 52 | - Espectro do TIADC com todos os desvios e sem compensação                    | 87 |

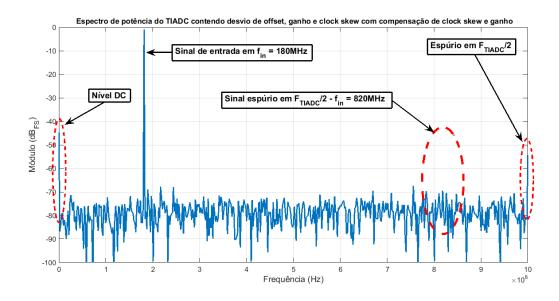

| FIGURA 53 | - Espectro do TIADC com todos os desvios e compensação do <i>clock skew</i> . | 87 |

| FIGURA 54 | - Espectro do TIADC com todos os desvios e compensação do <i>clock skew</i>   |    |

|           | e do ganho.                                                                   | 88 |

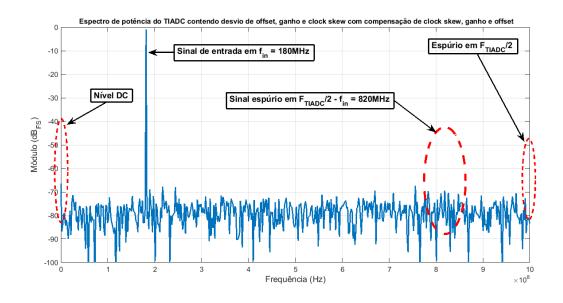

| FIGURA 55 | - Espectro do TIADC com todos os desvios e compensação de todos os            |    |

|           | desvios.                                                                      | 88 |

## LISTA DE TABELAS

| TABELA 1  | - Tabela de características do TIADC e sistema de compensação                      | 17 |

|-----------|------------------------------------------------------------------------------------|----|

| TABELA 2  | - Tabela comparativa dos métodos de compensação                                    | 31 |

| TABELA 3  | - Tabela comparativa dos métodos de projeto de FDF                                 | 47 |

| TABELA 4  | - Tabela de comparação entre as estruturas de Farrow com filtro GLS                | 80 |

| TABELA 5  | - Tabela de comparação do desempenho do TIADC antes e depois da                    |    |

|           | compensação de <i>clock skew</i> em 180MHz                                         | 81 |

| TABELA 6  | - Tabela de comparação do desempenho do TIADC antes e depois da                    |    |

|           | compensação de ganho em 180MHz.                                                    | 83 |

| TABELA 7  | - Tabela de comparação do desempenho do TIADC antes e depois da                    |    |

|           | compensação de <i>offset</i> em 180MHz.                                            | 85 |

| TABELA 8  | - Tabela de comparação do desempenho do TIADC antes e depois do                    |    |

|           | sistema completo de compensação em 180MHz                                          | 89 |

| TABELA 9  | - Tabela de utilização de recursos e desempenho dos estimadores e                  |    |

|           | compensadores de desvio.                                                           | 89 |

| TABELA 10 | - Tabela de utilização de recursos para o projeto utilizando <i>FPGA In Loop</i> . | 90 |

| TABELA 11 | - Tabela de comparação do desempenho do TIADC antes e depois do                    |    |

|           | sistema completo de compensação em 180MHz. Teste com FPGA In Loop.                 | 90 |

#### LISTA DE SIGLAS

ADC Analog to Digital Converter

AFB Advanced Filter Bank

DC Direct Current

DSP Digital Signal Processing

ENOB Effective Number of Bits

FDF Filtro de Delay Fracionário

FFT Fast Fourier Transform

FIL FPGA In Loop

FIR Finite Impulse Response FPGA Field Programable Gate Array

FS Full Scale GHz Gigahertz

GLS Generalized Least Square

HDL Hardware Description Language

JTAG Joint Test Action Group

LS Least Square LUT Look Up Table

MCM Multiple Constant Multiplication

MHz Megahertz

MS/s Mega Samples per Second

RF Rádio frequência RMS Root Mean Square RSS Root Sum Square

SDR Software Defined Radio SFDR Spurios Free Dynamic Range

SINAD Signal to Noise and Distortion Ratio

SNR Signal to Noise Ratio

TIADC Time Interleaved Analog to Digital Converter

USB Universal Serial Bus VDL Variable Delay Line

VHDL Very high speed integrated circuit Hardware Description Language

### LISTA DE SÍMBOLOS

M Número de ADCs de um TIADC

$F_{ADC}$  Frequência de amostragem de um ADC do TIADC

$F_{TIADC}$  Frequência de amostragem do TIADC

$T_s$  Intervalo de amostragem  $F_s$  Frequência de amostragem  $\delta(t)$  Função Dirac ou impulso x(t) Sinal contínuo no tempo

t Variável de tempo p(t) Função Dirac periódica

$x_p(t)$  Sinal contínuo amostrado no tempo

$\omega_s$  Frequência de amostragem em radianos por segundo

$X_p(j\omega)$  Transformada de Fourier de  $x_p(t)$

*ω* Frequência angular

$X(j\omega)$  Transformada de Fourier de x(t)  $\omega_m$  Frequência angular do sinal x(t) $x_q$  Sinal x(t) quantizado na amplitude

$N_b$  Número de *bits*

$q_a$  Quantum de um ADC

$e_q$  Erro de quantização do ADC

$e_q(t)$  Erro de quantização do ADC em função do tempo

s Inclinação da reta da onda dente-de-serra

r Ruído de quantização

*RMS*<sub>sinal</sub> Valor RMS do sinal de entrada de um ADC

$RSS_{ruido}$  Valor RSS de todos os componentes espectrais presentes na saída de um ADC,

excluindo-se o sinal de entrada e o nível DC

dB Decibéis

Banda espectral de um sinal

dBFS Decibéis em relação ao fundo de escala

*CLK*<sub>i</sub> Iésimo sinal de *clock* para controle da amostragem de um TIADC

x[n] Sinal x(t) discretizado no tempo

*n* índice da amostra

$f_{offset}$  Frequência do tom espúrio do TIADC devido ao desvio de offset

k Variável de índice

$f_{ganho}$  Frequência do tom espúrio do TIADC devido ao desvio de ganho

$f_{in}$  Frequência do sinal senoidal de entrada do TIADC  $\Delta T_s$  Diferença no intervalo de amostragem em relação a  $T_s$

$\Delta V$  Diferença na amplitude do valor amostrado devido ao desvio de *clock skew*

$\Delta t$  Erro no instante de aquisição de um dos canais de um TIADC

y(n) Sinal discreto no tempo saída do TIADC  $f_0$  Sinal senoidal de entrada do TIADC  $T_{TIADC}$  Intervalo de amostragem do TIADC

$\phi$  Fase do sinal de entrada do TIADC, em radianos h(t) Função no tempo contínuo do filtro ideal de atraso

$t_l$  Intervalo de tempo contínuo em que o sinal de entrada de h(t) é atrasado

y(t) Sinal contínuo no tempo de saida de um sistema  $h(nT_s)$  Função no tempo discreto do filtro ideal de atraso

D Atraso total de um sinal

$x(nT_s)$  Sinal x(t) amostrado com um intervalo de tempo  $T_s$   $y(nT_s)$  Sinal y(t) amostrado com um intervalo de tempo  $T_s$

$Y(j\omega)$  Transformada de Fourier de y(t) $H(j\omega)$  Função de transferência de h(t)

$\Phi_{H(i\omega)}$  Fase de  $H(j\omega)$

$\tau_{H(j\omega)}$  Atraso de fase de  $H(j\omega)$

$H_{ap}(j\omega)$  Função de transferência do filtro de aproximação de  $h(nT_s)$

$E(e^{j\omega})$  Erro de aproximação de  $H_{ap}(j\omega)$  $E_2$  Integral de erro quadrático

$h_{ap}(n)$  Resposta ao impulso do filtro discreto de aproximação do filtro ideal h(n)

N Ordem de um filtro

$M_i$  índice do primeiro valor diferente de zero na resposta ao impulso de um filtro

$\alpha$  Parâmetro da largura de banda passante  $W(\omega)$  Função peso no domínio da frequência h Vetor dos coeficientes do filtro FIR e Vetor de exponenciais complexas

P Matriz de coeficientes para o projeto de filtros GLS

p<sub>1</sub> Vetor de coeficientes para o projeto de filtros GLS

K Constante inteira

$\Omega_k$  Frequência angulas onde a magnitude do filtro é zero (filtro Minimax)

$E_{\Omega}$  Matriz de exponenciais complexas em  $\Omega_k$   $\mathbf{e_D}$  Vetor de exponenciais complexas em  $D\Omega_k$   $\mathbf{P}_{\Omega}$  Matriz da parte real e imaginária de  $E_{\Omega}$  $\mathbf{p}_{\Omega}$  Matriz da parte real e imaginária de  $\mathbf{e_D}$

Q Constante inteiraμ Delay fracionário

$M_O$  Ordem polinomial da estrutura de Farrow

$C_m(n)$  Vetor de coeficientes do m-ésimo filtro FIR da estrutura de Farrow

$h_m(n)$  Filtro composto dos coeficientes polinomiais em m da estrutura de Farrow

x Variável real

*a<sub>n</sub>* Variável de coeficiente real

y Variável real q Índice inteiro

z Variável da transformada z

$H_m(z)$  Função de transferência do filtro  $h_m(n)$

V Matriz de Vandermondec Vetor de coeficientes em z

## SUMÁRIO

| 1 IN  | TRODUÇÃO                                                  | 15        |

|-------|-----------------------------------------------------------|-----------|

|       |                                                           | 15        |

|       |                                                           | 16        |

| 1.2.1 | Objetivo Geral                                            | 16        |

| 1.2.2 | Objetivos Específicos                                     | 16        |

|       | STRUTURA DA DISSERTAÇÃO                                   | 17        |

|       |                                                           | 18        |

| 2.1 C | CONCEITOS GERAIS                                          | 18        |

|       | Introdução e conceito de amostragem                       | 18        |

|       |                                                           | 19        |

|       | Métricas de desempenho para conversores analógico digital | 21        |

| II    | NTERCALADO                                                | 23        |

|       | DESVIOS DO CONVERSOR ANALÓGICO DIGITAL INTERCALADO        | 24        |

|       |                                                           | 24        |

|       |                                                           | 25        |

|       |                                                           | 27        |

|       |                                                           | 29        |

| 2.4.1 |                                                           | 32        |

|       |                                                           | 32        |

|       |                                                           | 32        |

|       |                                                           | 34        |

|       |                                                           | 34        |

|       |                                                           | 36        |

|       |                                                           | 39        |

|       |                                                           | 42        |

|       | · ·                                                       | 44        |

|       |                                                           | 46        |

|       |                                                           | 47        |

|       |                                                           | 52        |

| 4.1 M | MODELAGEM DO TIADC                                        | 53        |

|       | ž.                                                        | 54        |

|       | •                                                         | 55        |

|       |                                                           | 63        |

|       |                                                           | 64        |

|       |                                                           | 66        |

|       | Metodologia de desenvolvimento                            | 66        |

|       |                                                           | 69        |

|       |                                                           | <b>73</b> |

|       |                                                           | 73        |

|       |                                                           | 82        |

| 5.3 | OFFSET                                                   | ę |

|-----|----------------------------------------------------------|---|

| 5.4 | SISTEMA COMPLETO                                         |   |

| 5.5 | SIMULAÇÃO COM FPGA IN LOOP                               |   |

|     | CONCLUSÕES E TRABALHOS FUTUROS                           |   |

| REF | FERÊNCIAS                                                |   |

| Anê | ndice A – DEDUÇÃO MATEMÁTICA DA IMAGEM NA SAÍDA DO TIADC |   |

## 1 INTRODUÇÃO

## 1.1 MOTIVAÇÃO

Nos modernos receptores de rádio frequência (RF) digitais para aplicações móveis são necessárias ao menos duas translações de frequência para o início do processo de demodulação do sinal. A translação da frequência de portadora do sinal RF para uma frequência intermediária aumenta a complexidade dos circuitos utilizados nos receptores. Estes circuitos também apresentam limitações de desempenho tais como limitação do *range* dinâmico e adição de ruído (RIVET et al., 2010).

Uma solução interessante para este problema está no conceito de *rádio definido por software* (SDR, *Software Defined Radio*) proposta por Mitola (MITOLA, 2000), que consiste em uma estrutura de receptor formada por uma antena, um conversor analógico digital (ADC, *Analog to Digital Converter*) e um bloco de processamento digital de sinais (DSP, *Digital Signal Processing*). Neste conceito em que o ADC é colocado logo após a antena, funções como filtros e *mixers* analógicos são implementadas digitalmente no bloco DSP. Entretanto, nesta topologia o ADC torna-se um ponto crítico do sistema, já que deste é requerida uma elevada taxa de amostragem e elevada resolução (VOGEL; JOHANSSON, 2006).

É neste contexto que a estrutura do Conversor Analógico Digital Intercalado (TIADC, *Time Interleaved Analog to Digital Converter*) surge como uma interessante solução (RAZAVI, 2013). A estrutura do TIADC consiste na aquisição do sinal de entrada por um número M de ADCs paralelos, cada qual adquirindo o sinal de entrada à uma taxa de amostragem de  $F_{ADC}$ .

Cada ADC adquire o sinal de entrada em instante diferente dos demais, de forma intercalada no tempo, gerando na saída do sistema um sinal equivalente com taxa de amostragem  $F_{TIADC} = M \cdot F_{ADC}$ . Idealmente, o desempenho do TIADC, que pode ser indicado por métricas tais como o SNR (*Signal to Noise Ratio*) e o SFDR (*Spurios Free Dynamic Range*), é similar a dos seus ADCs constituintes. Mas, devido a desvios no instante de aquisição (*clock skew*) e no casamento do ganho e *offset* individual de cada conversor, o desempenho é degradado (VOGEL; JOHANSSON, 2006) (RAZAVI, 2013).

Entretanto, os problemas oriundos dos circuitos analógicos destes conversores podem ser tratados digitalmente (ROERMUND et al., 2005). A compensação digital destes desvios possui complexidade significativa, em especial para a compensação do *clock skew*, sendo esta uma área de intensa pesquisa.

#### 1.2 OBJETIVOS

#### 1.2.1 OBJETIVO GERAL

O principal objetivo deste trabalho foi implementar e validar em FPGA (*Field Programable Gate Array*) sistemas digitais de compensação dos desvios do TIADC, responsáveis pela degradação do desempenho do conversor. A validação destes sistemas é realizada com a sua implementação em FPGA, e simulação dos sinais resultantes do TIADC em *software*.

A implementação e validação do sistema de compensação em FPGA permitirá então a sua futura inserção em um circuito integrado de um TIADC.

#### 1.2.2 OBJETIVOS ESPECÍFICOS

Os objetivos específicos deste trabalho foram:

- Modelar o TIADC e os sistemas digitais de compensação utilizando software Simulink.

- Avaliar o desempenho de diferentes métodos de projeto de filtros de atraso fracionário utilizando aritmética de ponto fixo.

- Gerar código HDL (*Hardware Description Language*) para síntese em FPGA dos sistemas digitais de compensação.

- Utilizar uma interface entre o modelo do TIADC em Simulink e o sistema sintetizado em FPGA para validação.

- Validar os sistemas de compensação em FPGA, utilizando um modelo comportamental do TIADC em Simulink para isto.

O TIADC que será modelado conterá dois ADCs, cada um operando com uma frequência de amostragem  $F_{ADC}$  de 1 GHz e com resolução de 8 *bits*. A frequência de amostragem do TIADC ( $F_{TIADC}$ ) será portanto 2 GHz. A banda mínima de interesse que

será considerada para o TIADC é de 200 MHz, ou seja, espera-se que o TIADC realize o *oversampling* do sinal de entrada. Como será discutido no capítulo 2, a operação de um ADC com *oversampling* do sinal de entrada permite obter ganhos no seu desempenho. O sistema de compensação que será implementado deverá compensar os desvios do TIADC ao menos para esta banda mínima de interesse. As características desejadas do TIADC e do sistema de compensação são então resumidas na tabela 1.

Tabela 1: Tabela de características do TIADC e sistema de compensação.

| Descrição da característica                    | Valor   |

|------------------------------------------------|---------|

| Número de ADCs                                 | 2       |

| Frequência de amostragem de cada ADC           | 1 GHz   |

| Resolução do ADC                               | 8 bits  |

| Frequência de amostragem do TIADC              | 2 GHz   |

| Frequência máxima do sinal de entrada do TIADC | 200 MHz |

Fonte: Autoria própria

## 1.3 ESTRUTURA DA DISSERTAÇÃO

Esta dissertação é dividida em seis capítulos. No segundo capítulo são apresentados os conceitos básicos do TIADC, a formulação teórica dos desvios e seu impacto no desempenho do sistema, assim como é realizada uma revisão da literatura com os principais métodos de compensação dos desvios. No terceiro capítulo o conceito dos filtros de *delay* fracionário e a estrutura de Farrow são apresentados. Os conceitos mostrados nestes dois capítulos são essenciais para a compreensão da estrutura de compensação implementada nos capítulos seguintes. O quarto capítulo descreve os modelos comportamentais do TIADC e a estrutura de compensação em Simulink. Este capítulo apresenta também a descrição da conversão dos modelos comportamentais em código HDL e a interface de teste entre a FPGA e o Simulink. Os resultados obtidos com estas estruturas e o uso de recursos de *hardware* utilizados em FPGA são apresentados no quinto capítulo. E, finalmente, no sexto capítulo são apresentadas as conclusões finais e propostas para futuros trabalhos.

#### 2 CONVERSOR ANALÓGICO DIGITAL INTERCALADO

#### 2.1 CONCEITOS GERAIS

### 2.1.1 INTRODUÇÃO E CONCEITO DE AMOSTRAGEM

O conversor analógico digital é o dispositivo que converte sinais analógicos contínuos no tempo em sinais digitais discretizados no tempo. A conversão do sinal analógico em digital no ADC pode ser entendida como dois processos distintos: amostragem e quantização. O primeiro processo, a amostragem, consiste na discretização no tempo do sinal. A amostragem do sinal ocorre em intervalos igualmente espaçados no tempo,  $T_s$ , ou similarmente, a uma frequência  $F_s$ . Se respeitado o teorema da amostragem (OPPENHEIM et al., 1996), a sequência de amostras obtidas do sinal o representa de forma unívoca. Uma forma conveniente de representar a amostragem é utilizar um trem de impulsos (função Dirac  $\delta(t)$ ) periódico multiplicado pelo sinal analógico. Considere o sinal analógico x(t) (contínuo no tempo t) e a função Dirac periódica p(t), com período de amostragem  $T_s$ . Então o sinal amostrado  $x_p(t)$  pode ser representado por:

$$x_p(t) = p(t)x(t) \tag{1}$$

onde,

$$p(t) = \sum_{n = -\infty}^{\infty} \delta(t - nT_s). \tag{2}$$

Aplicando-se (2) em (1) pode-se representar o sinal  $x_p(t)$  pela equação:

$$x_p(t) = \sum_{n=-\infty}^{\infty} x(nT_s)\delta(t - nT_s).$$

(3)

Aplicando-se a transformada de Fourier à equação (3) é obtido:

$$X_{p}(j\boldsymbol{\omega}) = \frac{1}{2\pi} [X(j\boldsymbol{\omega}) * P(j\boldsymbol{\omega})] = \frac{1}{2\pi} [X(j\boldsymbol{\omega}) * \frac{2\pi}{T_{s}} \sum_{k=-\infty}^{\infty} \delta(\boldsymbol{\omega} - k\boldsymbol{\omega}_{s})], \tag{4}$$

onde  $\omega_s = Fs/2\pi$ . Como a convolução de um sinal por um impulso o desloca no eixo do tempo, ou no eixo da frequência, é obtida a equação (5).

$$X_p(j\omega) = \frac{1}{T_s} \sum_{k=-\infty}^{\infty} X(j(\omega - k\omega_s)).$$

(5)

$X_p(j\omega)$  é uma função periódica em  $\omega$  constituída da superposição das réplicas deslocadas de  $X(j\omega)$  (OPPENHEIM et al., 1996). Para respeitar o *critério de Nyquist*, a maior frequência  $\omega_m$  de  $X(j\omega)$  deve ser menor do que  $\omega_s/2$ . Se esta condição não for respeitada ocorre o *aliasing* do sinal amostrado, a sobreposição no espectro das réplicas de  $X_p(j\omega)$ . Esta situação é denominada de *subamostragem* (ou *subsampling*). A condição inversa, quando a frequência de amostragem  $\omega_s$  é maior do que  $2\omega_m$ , é denominada *oversampling*. O *oversampling* permite um ganho de desempenho no processo de aquisição por parte do ADC. O segundo processo da conversão analógico digital, a quantização, será discutido na subseção seguinte.

### 2.1.2 QUANTIZAÇÃO

A quantização consiste na função de transferência que associa ao sinal analógico amostrado  $x(nT_s)$  um valor codificado  $x_q$  (denominado  $c\acute{o}digo$ ), sendo  $x_q$  restrito à um conjunto limitado de valores. A cada valor  $x_q$  obtido está associado um intervalo de amplitude de  $x(nT_s)$ . Este intervalo de amplitude é igualmente espaçado para todos os valores de  $x_q$  e a sua amplitude é chamada de *quantum*. Este representa a menor variação na amplitude do sinal de entrada que causa uma mudança no  $c\acute{o}digo$ . Normalmente o código é um número binário representado por  $N_b$  bits. O número  $N_b$  de bits utilizado para representar o código binário, e consequentemente o número de faixas representadas pelo ADC, é a resolução do conversor. O fundo de escala (FS,  $Full\ Scale$ ) do conversor é correlacionado com o quantum pela equação (6), onde  $q_a$  representa a amplitude do quantum e  $N_b$  representa o número de bits de resolução do ADC.

$$FS = q_a(2^{N_b} - 1). (6)$$

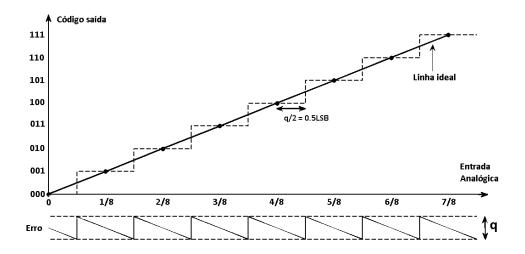

A figura 1 ilustra a função de transferência e a quantização do ADC.

A quantização introduz um erro sistemático no ADC, o erro de quantização. Este erro decorre da diferença entre a amplitude do sinal analógico de entrada e de sua saída digital. O erro de quantização  $e_q$  está contido no intervalo  $[-q_a/2;q_a/2]$  e, para qualquer sinal de frequência maior do que zero, pode ser aproximado por uma forma de onda dente-

Figura 1: Função de transferência de um ADC ideal e erro de quantização.

Fonte: Autoria própria

de-serra contendo uma amplitude pico-a-pico igual à  $q_a$  (KESTER, 2005). Considerando esta simplificação no modelo do erro de quantização, o mesmo pode ser expresso pela equação (7).

$$e_q(t) = st, \frac{-q_a}{2s} < t < \frac{q_a}{2s}. \tag{7}$$

Onde  $e_q(t)$  representa o erro de quantização e s representa a inclinação da reta da onda dente-de-serra. O erro médio quadrático de  $e_q(t)$  é dado pela equação (8).

$$\overline{e_q^2(t)} = \frac{s}{q_a} \int_{-\frac{q_a}{2s}}^{\frac{q_a}{2s}} (st)^2 dt \tag{8}$$

Resolvendo a integral da equação (8) e simplificando-a é obtida a equação (9).

$$\overline{e_q^2(t)} = \frac{q_a^2}{12}. (9)$$

E o valor RMS (Root Mean Square) do ruído de quantização (r) é dado pela equação (10).

$$\sqrt{r^2(t)} = \frac{q_a}{\sqrt{12}}. (10)$$

A análise simplificada do ruído de quantização o considera não correlacionado com o sinal de entrada, e que a distribuição estatística de probabilidade do erro de quantização é aproximadamente uniforme. Do exposto conclui-se que o erro de quantização é proporcional ao *quantum*  $q_a$ . Medições mais precisas de um ADC dependem portanto de um *quantum* menor, ou seja, de uma maior resolução do ADC.

### 2.1.3 MÉTRICAS DE DESEMPENHO PARA CONVERSORES ANALÓGICO DIGITAL

Para a adequada especificação e avaliação dos conversores analógico digitais são necessárias métricas de desempenho. Diversos aspectos dos ADCs devem ser avaliados antes de sua seleção ou especificação, onde a relevância de cada aspecto é dependente da aplicação. As principais métricas para análise que serão aqui consideradas são a *SNR* (*Signal to Noise Ratio*), a *SINAD* (*Signal to Noise and Distortion Ratio*), o *SFDR* (*Spurious Free Dynamic Range*) e o *ENOB* (*Effective Number of Bits*). A primeira delas, a SNR, é definida como a razão entre o valor RMS do sinal de entrada e o valor médio do RSS (*Root Sum Square*) de todos os demais componentes espectrais, excluindo as cinco primeiras harmônicas e o nível DC (KESTER, 2005). A SINAD é definida da mesma forma que a SNR, mas com a adição das cinco primeiras harmônicas do espectro. O cálculo da SINAD é dado por:

$$SINAD = 10log_{10} \frac{RMS_{sinal}}{RSS_{ruido}} dB, (11)$$

onde  $RMS_{sinal}$  é o valor RMS do sinal de entrada e  $RSS_{ruido}$  é o RSS de todos os demais componentes espectrais, exceto o nível DC.

Ambas as métricas são indicadores do desempenho dinâmico do ADC e, usualmente, ambas são fornecidas em unidades de dB (decibéis). Em um ADC ideal de  $N_b$  bits de resolução, onde somente o ruído de quantização está presente, a SNR para um sinal senoidal cujo a ampitude de pico é o fundo de escala do ADC é dada por:

$$SNR = 6,02N_b + 1,76dB (12)$$

Na forma apresentada na equação (12) é considerada toda a banda de Nyquist, ou seja, do nível contínuo do sinal até a frequência Fs/2. Em muitas aplicações o sinal de interesse pode ocupar uma banda BW menor do que Nyquist. Nestas aplicações é possível retirar o ruído externo à banda BW utilizando filtros digitais e aumentar o desempenho da SNR. Este aumento do desempenho na SNR é chamado de  $ganho\ de\ processo\ (KESTER, 2005)$  e pode ser incluído na equação (12), considerando que o ruído do ADC é branco, como:

$$SNR = 6,02N + 1,76 + 10log_{10} \frac{Fs}{2BW}.$$

(13)

O ganho de processo dado pela equação (13) é obtido com o uso de *oversampling* somente, sem a utilização de quaisquer outros componentes em conjunto com o ADC. Ganhos

na SNR maiores do que os obtidos na equação (13) podem ser obtidos do ADC quando este é utilizado em conjunto com um modulador Sigma-Delta (MARIANO, 2008).

O desempenho de um ADC real, entretanto, é inferior ao de um ADC ideal devido a outras fontes de ruído e erros no conversor, além do ruído de quantização. Uma forma de avaliar o desempenho de ADCs considerando estes ruídos é utilizando o ENOB. O ENOB permite a comparação do desempenho de um ADC real com relação à um ADC ideal, contendo um valor efetivo de bits. O valor de ENOB pode ser obtido da SINAD do ADC, substituindo a SNR na equação (12) pela SINAD e reorganizando-a em função de  $N_b$ . Desta forma o ENOB pode ser calculado pela equação (14).

$$ENOB = \frac{SINAD - 1,76dB}{6,02} \tag{14}$$

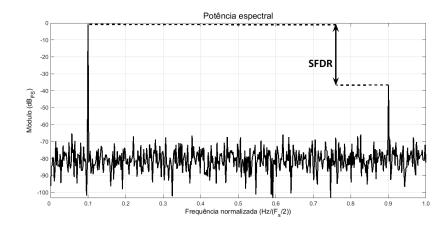

Em aplicações de ADCs para sistemas de comunicação o *SFDR* assume um significado especial. Este está relacionado com o menor sinal capaz de ser detectado (sensibilidade) por um receptor de rádio. O SFDR é definido como a razão da amplitude RMS do sinal de entrada pela amplitude do componente espectral espúrio de pico medido na banda de interesse (KESTER, 2005). Usualmente o SFDR é especificado em relação à um sinal que atinge o valor de fundo de escala do ADC, em *dBFS* (decibéis em relação ao fundo de escala).

Figura 2: Espectro de um ADC e seu respectivo SFDR (*Spurious Free Dynamic Range*). O eixo da frequência é normalizado em relação a frequência de amostragem  $F_s$ .

Fonte: Autoria própria

A figura 2 ilustra o espectro de um ADC e seu respectivo SFDR. Na figura 2 há um sinal de entrada que atinge o fundo de escala do ADC na frequência normalizada 0,1. O sinal de ruído espúrio de maior amplitude ocorre na frequência normalizada de 0,9. O SFDR neste exemplo será portanto menor do que 40 dBFS, pois esta é a diferença entre a amplitude do sinal

de entrada e o sinal espúrio de pico, como ilustrado pela seta dupla presente na figura.

# 2.2 PRINCÍPIO DE OPERAÇÃO DO CONVERSOR ANALÓGICO DIGITAL INTERCALADO

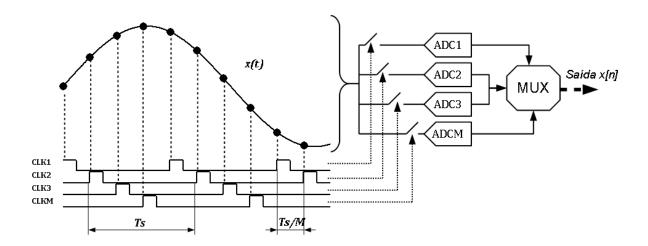

Considere o TIADC formado por M ADCs idênticos ilustrado na figura 3. Nesta estrutura cada um dos ADCs realiza uma amostragem do sinal de entrada contínuo no tempo x(t) na transição de borda positiva do sinal de  $clock\ CLK_i$ . Cada ADC possui o mesmo intervalo de tempo de aquisição  $T_s$ , mas as bordas de transição de clock estão defasadas no tempo por um intervalo de tempo  $T_s/M$ . O sinal digital de saída dos conversores é interligado a um multiplexador, e da saída deste é obtido o sinal x[n] formado pelas amostras intercaladas no tempo dos M ADCs. A saída x[n] possui um intervalo de tempo de aquisição  $T_s/M$ , ou seja, a frequência de aquisição  $F_{TIADC}$  do TIADC é igual à  $M \cdot F_{ADC}$ .

Figura 3: Estrutura do TIADC com o detalhamento do controle dos instantes de aquisição. No lado esquerdo da figura o sinal x(t) é amostrado pelos M ADCs, à direita. O instante de aquisição destes ADCs são controlados pelo sinal de clock CLK1, CLK2, ..., CLKM. Na saída dos ADCs é interligado um multiplexador.

Fonte: Autoria própria

A principal vantagem do TIADC está na obtenção de maiores taxas de amostragem a partir de múltiplos ADCs que operam a taxas de amostragem menores. Desta forma esta estrutura pode ser aplicada em qualquer topologia de ADC para a obtenção de taxas de amostragem elevadas, inclusive além do que seria possível utilizando um único ADC (BLACK JR.; HODGES, 1980). A estrutura foi originalmente proposta por *Black* e *Hodges* com o objetivo de reduzir a área de ADCs do tipo *flash* de alta velocidade. Mas foi a pesquisa de (SUMANEN et al., 2001), um TIADC de quatro canais com 280mW de potência a uma taxa

de amostragem de 200 MS/s (*Mega Samples per Second*), que atraiu o interesse acadêmico para a sua aplicação. O aspecto que não havia sido explorado anteriormente é a relação custo benefício que existe entre a potência dissipada por esta estrutura em comparação com a sua taxa de amostragem (RAZAVI, 2013). A vantagem do TIADC deve-se ao fato de que os amplificadores operacionais dos conversores, quando são consideradas taxas de amostragem próximas do limite de banda dos amplificadores, possuem aumento de potência quadrático com relação ao aumento da taxa de amostragem (SUMANEN et al., 2001). Operar os sub-ADCs a taxas de amostragem menores mantêm a relação entre o aumento de potência e a taxa de amostragem linear.

#### 2.3 DESVIOS DO CONVERSOR ANALÓGICO DIGITAL INTERCALADO

Idealmente o desempenho do TIADC é idêntico ao desempenho de seus sub-ADCs constituintes. Entretanto, devido a diferenças intrínsecas no *offset*, no *ganho* e no *instante de amostragem* (*clock skew*) entre os sub-ADCs, o desempenho do TIADC é degradado. Estas diferenças aparecem no espectro do sinal amostrado como *imagens*, sinais espúrios de erro, que ocorrem em frequências dependentes da taxa de amostragem do TIADC e do sinal de entrada. Nesta seção estes *desvios* do TIADC e seus efeitos são explanados.

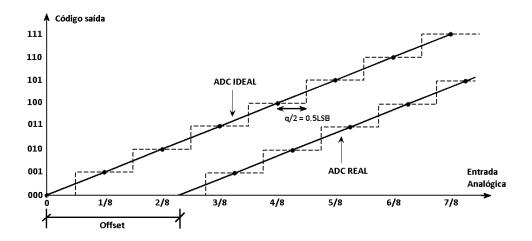

#### 2.3.1 OFFSET

A função de transferência de um ADC real contêm um erro constante, chamado de *offset*. Para um único conversor este erro é estático. Na figura 4 a função de transferência de um ADC com *offset* é representada.

Entretanto, em um TIADC o *offset* de cada sub-ADC é diferente, gerando assim um sinal de erro periódico. Este sinal de erro periódico é independente do sinal de entrada no domínio do tempo e da frequência (KUROSAWA et al., 2001), possuindo tons espúrios no espectro do TIADC nas frequências:

$$f_{offset} = k \frac{F_{TIADC}}{M}, \quad k = 1, 2, ..., M.$$

(15)

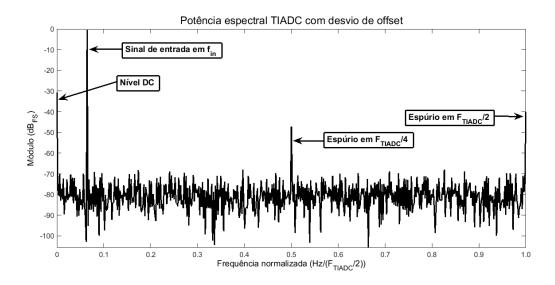

A figura 5 ilustra o espectro de um TIADC contendo somente o desvio de *offset*. Nesta figura é apresentada a potência espectral obtida da aquisição de um TIADC de quatro canais. Pode-se observar no espectro o sinal senoidal de entrada, identificado na figura, e os sinais espúrios resultantes do desvio de *offset*.

Figura 4: Função de transferência de um ADC com *offset*Fonte: Autoria própria

Figura 5: Espectro de um TIADC de 4 canais contendo somente o desvio de *offset*. O espectro está normalizada em relação a  $F_{TIADC}/2$ .

Fonte: Autoria própria

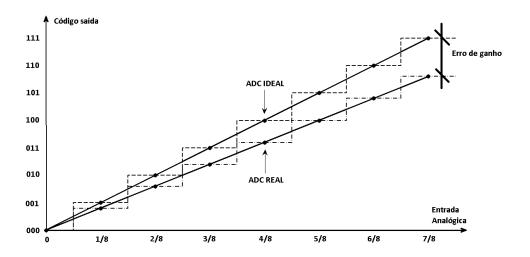

#### 2.3.2 GANHO

A inclinação da reta da função de transferência de um ADC real é diferente de seu valor nominal, havendo assim um erro de *ganho* do conversor. Esta diferença na função de transferência é ilustrada pela figura 6. Em um TIADC cada sub-ADC pode possuir um ganho real diferente dos demais. Esta diferença no ganho dos sub-ADCs gera um sinal espúrio de erro na saída do TIADC, com picos nas frequências dadas pela equação (16).

$$f_{ganho} = \pm f_{in} + k \frac{F_{TIADC}}{M}, \quad k = 1, 2, ..., M.$$

(16)

Figura 6: Função de transferência de um ADC real com desvio no valor de ganho Fonte: Autoria própria

Onde  $f_{in}$  é a frequência do sinal de entrada do TIADC. O erro devido as diferenças de ganho no TIADC é modulado em amplitude pelo sinal de entrada (KUROSAWA et al., 2001). Desta forma, a magnitude no domínio da frequência destes sinais espúrios depende da amplitude do sinal de entrada. Deve-se observar que as frequências em que os sinais espúrios ocorrem não dependem da amplitude do sinal de entrada, somente de sua frequência. A degradação no desempenho do TIADC (observada através de seu SNR) pelo desvio de ganho é constante em função da frequência de entrada do sinal (KUROSAWA et al., 2001). A figura 7 ilustra o espectro de um TIADC, com 4 sub-ADCs, contendo somente o desvio de ganho.

Figura 7: Espectro de um TIADC de 4 canais contendo somente o desvio de ganho. O espectro está normalizado em relação a  $F_{TIADC}/2$ .

Fonte: Autoria própria

#### 2.3.3 CLOCK SKEW

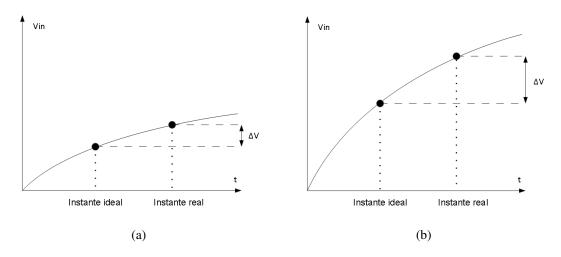

O desempenho de conversores analógico digital também é degradado por erros no instante de aquisição do sinal analógico. Os principais erros são o aperture jitter e o aperture delay. O aperture jitter é um erro randômico, amostra por amostra, no instante de aquisição do sinal de entrada, causado por diversas fontes de ruído (ruído térmico, ruído da fonte de alimentação, etc) (MARIANO, 2008). O seu efeito sobre o conversor é a degradação do SNR do sinal adquirido. Já o aperture delay é um erro constante no ADC causado pelo atraso entre o comando de amostragem do sinal de entrada e o instante em que efetivamente o sinal é amostrado (MARIANO, 2008). Para compreensão do efeito do aperture delay considere o sinal contínuo x(t), amostrado por um ADC com intervalo de amostragem  $T_s$ . Idealmente a saída y(n) deste ADC será o sinal amostrado  $x(nT_s)$ . Se entretanto, houver um erro  $\Delta T_s$  no intervalo de amostragem, a saída y(n) será dada por  $x(n(T_s + \Delta T_s))$ , gerando uma diferença  $\Delta V = x(n(T_s + \Delta T_s)) - x(nT_s)$  na amplitude do sinal de saída. Esta diferença de amplitude será maior quanto maior for o erro  $\Delta T_s$  e a derivada do sinal x(t), como é ilustrado pela figura 8. Como sinais de maiores frequências possuem derivada proporcionalmente maiores, pode-se concluir que o efeito do aperture delay será mais significativo em frequências elevadas.

Figura 8: Diferença na amplitude do sinal amostrado devido ao *aperture delay* para um sinal (a) de derivada baixa e (b) de derivada elevada.

Fonte: Autoria própria

Em um TIADC as diferenças no delay de cada sub-ADC produz tons espúrios no espectro do sinal de saída, nas mesmas frequências dadas pela equação (16). Esta fonte de erro do TIADC é chamada de *clock skew*. Em (JAMAL et al., 2004) um TIADC de dois canais, contendo um erro  $\Delta t$  no instante de aquisição de um dos canais, é utilizado para a dedução do sinal de saída y(n) do TIADC. Considere que  $x(t) = cos(2\pi f_0 t + \phi)$ , onde  $0 < 2\pi f_0 < \pi F_{TIADC}$ ,

e que x(t) é amostrado por um TIADC de dois canais em que  $T_{TIADC} = 1/F_{TIADC}$ . A saída y(n) do TIADC pode ser dada então pela equação (17) (a dedução desta equação é apresentada no Apêndice A).

$$y(n) = cos(\pi f_0 \Delta t) cos(2\pi f_0 T_{TIADC} + \pi f_0 \Delta t + \phi) +$$

$$sen(\pi f_0 \Delta t) sen((2\pi f_0 - \pi F_{TIADC}) n T_{TIADC} + \pi f_0 \Delta t + \phi)$$

(17)

Na equação (17) se  $\|\Delta t\| \ll T_{TIADC}$ ,  $cos(\pi f_0 \Delta t) \approx 1$  e  $sen(\pi f_0 \Delta t) \approx \pi f_0 \Delta t$ . Portanto esta equação pode ser simplificada para:

$$y(n) = cos(2\pi f_0 n T_{TIADC} + \pi f_0 \Delta t + \phi) - \pi f_0 \Delta t sen(2\pi (\frac{F_{TIADC}}{2} - f_0) n T_{TIADC} + \pi f_0 \Delta t + \phi)$$

$$\tag{18}$$

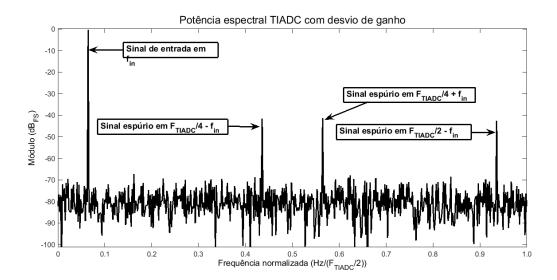

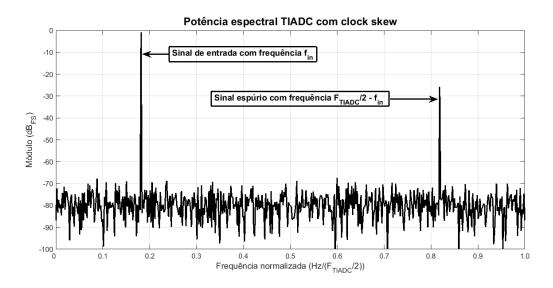

O primeiro termo da equação (18) refere-se ao sinal de entrada x(t) amostrado, o segundo termo refere-se ao sinal espúrio (chamado de *imagem*) decorrente do *clock skew*. Deste termo pode-se concluir que o sinal espúrio ocorre na frequência  $F_{TIADC}/2 - f_0$  e que, a sua amplitude é proporcional à frequência do sinal de entrada e ao erro  $\Delta t$ . A figura 9 ilustra o espectro deste TIADC de dois canais com o sinal amostrado e o sinal de imagem gerado.

Figura 9: Espectro do TIADC de dois canais com a presença do sinal espúrio gerado pelo *clock skew*.  $f_{in}$  é a frequência do sinal de entrada.

Fonte: Autoria própria

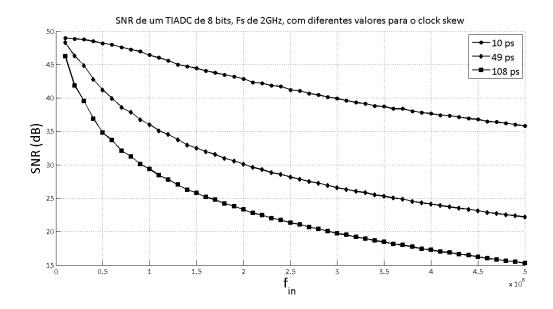

Comparado com o sinal de erro de ganho, o sinal de erro do *clock skew* possui um deslocamento de  $90^{\circ}$  com relação ao sinal de entrada (KUROSAWA et al., 2001). A degradação no SNR do sinal causada pelo *clock skew* aumenta com a frequência do sinal de entrada ( $f_{in}$ ), como pode ser visto pela figura 10.

Figura 10: SNR versus  $f_{in}$  de um TIADC com desvio de *clock skew* Fonte: Autoria própria

### 2.4 COMPENSAÇÃO DOS DESVIOS

A presença de tons espúrios no espectro do TIADC, devido aos desvios de *offset*, *ganho* e *clock skew*, degradam significativamente seu desempenho. Durante o projeto do circuito integrado, um *layout* cuidadoso do TIADC pode minimizar os seus efeitos (CONROY et al., ). Mas a eficácia desta abordagem é limitada (VOGEL; JOHANSSON, 2006). Desde a publicação de Black e Hodges (BLACK JR.; HODGES, 1980), diferentes métodos de compensação para cada um dos desvios do TIADC são apresentados na literatura.

A compensação dos desvios do TIADC pode ser dividida em duas partes: 1) estimação dos desvios, e 2) calibração, ou reconstrução do sinal de saída (VOGEL; JOHANSSON, 2006). A estimação dos desvios geralmente é realizada com o sinal de saída do TIADC. Do desvio estimado é gerado um sinal de controle para calibração, ou então, para a adequada reconstrução do sinal de saída. Os diferentes métodos de calibração podem ser classificados como: *online* e *offline*, que podem ser realizados em *foreground* ou *background*, com compensação *ativa* ou *passiva* (PARKEY; MIKHAEL, 2013). Entende-se por *online* os métodos que compensam os desvios com o TIADC em uso, atualizando estruturas e parâmetros, ou recalibrando, o TIADC de forma contínua ou periódica. *Offline* são os métodos que aplicam calibrações, ou pareamentos de características, no TIADC antes do seu uso na aplicação. *Softwares* que aplicam compensações nos dados obtidos do TIADC, na forma de um pós-processamento, e não verificam por variações temporais nos desvios do TIADC também são considerados *offline*.

Quando se faz necessário interromper o processo de conversão do TIADC para calibração, ou ajuste de parâmetros, e realizar estimativas dos desvios, (ou quando isto é feito sempre antes de ser iniciado o processo de amostragem) a compensação dos desvios ocorre em *foreground*. Este tipo de compensação é interessante para sistemas de instrumentação e testes, tais como osciloscópios. Quando a calibração, ou ajuste de parâmetros, e estimativas dos desvios ocorrem sem a interrupção da conversão do TIADC, a compensação ocorre em *background*. A compensação em *background* é necessária em aplicações de sistemas de comunicação, pois nestas aplicações geralmente o processo de conversão não pode ser interrompido (VOGEL; JOHANSSON, 2006).

Ainda pode-se dividir os métodos em *cegos*, ou *passivos*, quando não há informação prévia do sinal de entrada (na melhor das hipóteses os limites estatísticos do sinal são conhecidos), e em *não cegos*, ou *ativos*, quando é utilizado um sinal conhecido de entrada para calibração e estimação dos desvios. A tabela 2, modificada de (PARKEY; MIKHAEL, 2013), resume a classificação utilizada para os métodos de compensação, incluindo uma breve descrição das principais vantagens e desvantagens de cada categoria.

Tabela 2: Tabela comparativa dos métodos de compensação de desvios do TIADC

|          | Tabela 2: Tabela comparativa dos métodos de compensação de desvios do TIADC |            |            |              |          |                                                                                                                          |                                                                                                                              |                                                                                                                                                   |

|----------|-----------------------------------------------------------------------------|------------|------------|--------------|----------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Ativo    | Passivo                                                                     | Foreground | Background | Online       | Offline  | Exemplo                                                                                                                  | Vantagens                                                                                                                    | Desvantagens                                                                                                                                      |

| <b>√</b> |                                                                             | <b>√</b>   |            | V            |          | Instrumento que provê um modo de calibração ativado por <i>software</i> .                                                | Compensação dos desvios pode ser mais precisa com o uso de sinais de teste conhecidos e adequados.                           | Requer interrupção<br>do sistema e não<br>corrige variações<br>nos desvios ao<br>longo do tempo.                                                  |

|          |                                                                             |            | <b>√</b>   | $\checkmark$ |          | Injeção de um tom<br>em uma área livre<br>do espectro.                                                                   | Variações dos desvios rápidas e que ocorrem em períodos longos de tempo podem ser compensadas.                               | Limitado a correção dos desvios que podem ser medidos na frequência do tom especificado.                                                          |

| V        |                                                                             | <b>√</b>   |            |              | V        | Um sinal do tipo chirp é utilizado em produção para caracterização da resposta do TIADC.                                 | Permite redução da complexidade computacional requerida do TIADC ao utilizar compensação de desvios como estáticos.          | Cada sistema precisa ser testado individualmente e variações ao longo do tempo não são compensadas.                                               |

|          | <b>√</b>                                                                    | <b>√</b>   |            | <b>√</b>     |          | Um receptor de rádio recebe um preâmbulo de sincronização a cada pacote recebido e o utiliza para adaptar a compensação. | Disponibilidade<br>de um sinal<br>conhecido,<br>permitindo<br>adaptação mais<br>rápidas ou precisas<br>dos desvios.          | Adição de overhead na transmissão de mensagens e possibilidade de desempenho reduzido se não houver compensação adequada durante a sincronização. |

|          | <b>√</b>                                                                    |            | V          | <b>√</b>     |          | Um método cego adaptativo ajusta um filtro digital para compensar o clock skew.                                          | Nenhum sinal adicional é requerido. O filtro pode compensar variações rápidas ou que ocorram após um longo período de tempo. | A complexidade computacional pode ser elevada. Uma FPGA adicional pode ser requerida para a compensação.                                          |

|          | $\checkmark$                                                                | <b>√</b>   |            |              | <b>√</b> | Utilizando um sistema de teste durante a produção para calibração do TIADC.                                              | Não requer esforço computacional no TIADC.                                                                                   | Incapaz de se<br>adaptar a quaisquer<br>alterações nos<br>desvios.                                                                                |

Fonte: Modificado de (PARKEY; MIKHAEL, 2013)

#### 2.4.1 OFFSET

O desvio de *offset* é um dos mais simples de ser compensado digitalmente, pois requer somente o uso de somadores (VOGEL; JOHANSSON, 2006). O *offset* pode ser estimado a partir do valor médio do sinal de entrada de cada sub-ADC (VOGEL, 2005). O uso de um circuito de *chopper* randômico na entrada do TIADC para estimativa e compensação do *offset* é apresentado em (JAMAL et al., 2002) e em (EKLUND; GUSTAFSSON, 2000). O circuito analógico do *chopper* de entrada foi implementado em circuitos integrados em ambos os casos. Porém os circuitos digitais de compensação foram implementados em Matlab ou em DSP.

#### 2.4.2 GANHO

A compensação de ganho requer somente um multiplicador no canal à ser compensado (VOGEL; JOHANSSON, 2006). Métodos adaptativos, para operação em *background*, foram propostos na literatura para estimar o desvio de ganho em (JAMAL et al., 2004),(DYER et al., 1998),(FU et al., 1998). Jamal propôs um método de compensação e estimação do desvio totalmente digital. A implementação do método porém foi realizada somente em *software*. Em (DYER et al., 1998) o compensador de ganho é implementado utilizando circuitos mistos para um TIADC com frequência de amostragem de 40 MHz. Os mesmos autores de (DYER et al., 1998) implementam métodos de compensação de ganho totalmente digitais em (FU et al., 1998). Nos dois casos os métodos foram implementados em circuitos integrados. Uma abordagem diferente, baseada em propriedades ortogonais dos sinais, é apresentada em (FERRÉ et al., 2008).

#### 2.4.3 CLOCK SKEW

Os métodos para compensação do *clock skew* requerem soluções de maior complexidade, e apresentam seus próprios desafios (RAZAVI, 2013). Apesar de ser possível eliminar o *clock skew* com o uso de um *sample-and-hold* na entrada do TIADC (DYER et al., 1998), (SUMANEN et al., 2001), esta solução implica em aumento de potência e em aumento de ruído no sinal do TIADC (STEPANOVIC, 2012). Para estimar e calibrar o *clock skew* (POULTON et al., 2003) utiliza a injeção de um sinal conhecido no TIADC, e obtém estimativas do desvio através da FFT (*Fast Fourier Transform*) do sinal amostrado. *Advanced Filter Bank* (*AFB*) foi utilizado em (SEO et al., 2005) como um método *offline* para compensação de *clock skew*. Apesar de ter sido utilizado comercialmente com sucesso (LOONEY, 2003), o método requer múltiplos filtros FIR (*Finite Impulse Response*) longos (até 61-*taps* em (SEO

et al., 2005)). Em (SEO et al., 2005) os métodos de compensação são implementados em *software* somente. O método também possui o seu desempenho degradado devido a variações que possam ocorrer no *clock skew* ao longo do tempo.

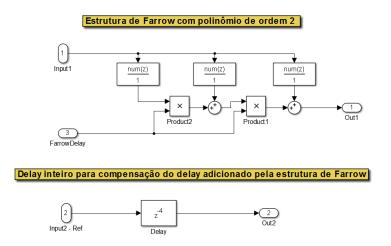

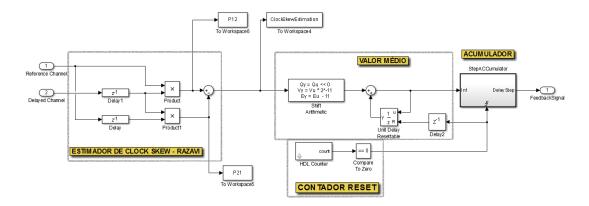

Em (JAMAL et al., 2002) um filtro de delay fracionário é utilizado para compensação dos desvios. Johansson (JOHANSSON; LOWENBORG, 2002), (JOHANSSON et al., 2006) construiu a base teórica para o uso de filtros de delay fracionário, e da estrutura de Farrow (FARROW, 1988), para compensação do *clock skew*. O uso de filtros de *delay* fracionário e da estrutura de Farrow, que permite o ajuste do desvio de tempo sem o recálculo de coeficientes de filtros, é um dos métodos mais populares para a reconstrução da saída do TIADC em virtude do clock skew. O método proposto por Johansson entretanto exige a operação do TIADC em oversampling. Este é no máximo igual a 2 e ocorre quando o TIADC possui um número par de ADCs. Em (RAZAVI, 2013) um estimador de baixa complexidade de implementação, baseado na autocorrelação do sinal de saída do TIADC, é utilizado em conjunto de um VDL (Variable Delay Line). Razavi implementou em um circuito integrado a compensação utilizando VDL. Entretanto, o estimador foi implementado em Matlab, utilizando a saída de um TIADC após o downsampling do seu sinal de saída. O ajuste analógico do delay no sample-and-hold em cada sub-ADC individual também é utilizado em (EL-CHAMMAS; MURMANN, 2011) e em (HUANG et al., 2011). A vantagem deste método sobre a compensação digital está no menor consumo de potência das estruturas VDL. Entretanto o VDL adiciona ruído na fase do sinal, o que causa um efeito no espectro do TIADC similar ao efeito do jitter. Os menores níveis de controle destas estruturas são da ordem de femtosegundos, o que pode ser relativamente complexo de ser obtido através de circuitos analógicos.

Os métodos de compensação digitais possuem as vantagens dos sistemas digitais de processamento de sinal. Em especial pode-se citar o controle do ruído adicionado ao sinal e a invariabilidade do ruído em função de interferências externas ao circuito, tais como variações de temperatura e tensões de alimentação. A tendência na utilização de sistemas digitais para melhorar o desempenho de conversores analógico-digital já foi apontada em (ROERMUND et al., 2005), denominado-os como conversores inteligentes. A compensação do desvio de *clock skew* através de filtros de *delay* fracionário é um dos principais exemplos dos ganhos obtidos com o uso de conversores inteligentes.

# 3 FILTROS DE DELAY FRACIONÁRIO

## 3.1 FILTROS DE DELAY FRACIONÁRIO

Considere o sinal contínuo no tempo x(t) como entrada de um filtro h(t) ideal, que atrasa o sinal x(t) por um intervalo de tempo  $t_l$  em sua saída y(t). A saída y(t) deste filtro é expressa pela equação (19).

$$y(t) = x(t - t_l). \tag{19}$$

Agora, considere que o sinal x(t) é uniformemente amostrado, com um intervalo de tempo  $T_s$ . Sendo  $h(nT_s)$  um filtro discreto que adiciona um atraso (delay) D ao sinal  $x(nT_s)$ , a saída  $y(nT_s)$  deste filtro será dada por:

$$y(nT_s) = x((n-D)T_s). (20)$$

Onde n representa o índice da amostra. Um valor de delay inteiro para este filtro, múltiplo do intervalo de amostragem  $T_s$ , é facilmente obtido através de elementos de memória das amostras anteriores (DIAZ-CARMONA; DOLECEK, 2011). Mas, se ao invés de um delay inteiro D for necessário um delay não múltiplo do intervalo de amostragem, a saída  $y(nT_s)$  será um valor entre duas amostras de x(t). Por não possuir este valor entre as amostras de  $x(nT_s)$ , o valor  $y(nT_s)$  somente pode ser obtido através da interpolação das amostras de  $x(nT_s)$  (LAAKSO et al., 1996). A interpolação das amostras pode ser realizada por um filtro de delay fracionário (FDF), um tipo de filtro digital capaz de atrasar um sinal por um intervalo de tempo não múltiplo do intervalo de amostragem. Idealmente este filtro deve manter a amplitude do sinal e deslocá-lo de uma unidade de tempo fracionária D. Dada a transformada de Fourier de x(t) como  $x(j\omega)$ , pode-se representar a transformada de Fourier  $y(j\omega)$  de y(t) como:

$$Y(j\omega) = X(j\omega)e^{-j\omega D}.$$

(21)

A função de transferência  $H(j\omega)$  deste filtro será portanto:

$$H(j\omega) = \frac{Y(j\omega)}{X(j\omega)} = \frac{X(j\omega)e^{-j\omega D}}{X(j\omega)} = e^{-j\omega D}.$$

(22)

Da equação (22) pode-se concluir que a magnitude do filtro é sempre unitária e que a fase deverá ser linear, sendo dada por:

$$\Phi_{H(i\omega)} = -D\omega. \tag{23}$$

E o atraso de fase  $\tau_{H(j\omega)}$  deste filtro é expresso pela equação (24). O atraso de fase é uma medida útil para expressar o tempo de atraso que um sinal de entrada sofre quando aplicado em um sistema linear.

$$\tau_{H(j\omega)} = -\frac{\Phi_{H(j\omega)}}{\omega} = -\frac{-D\omega}{\omega} = D. \tag{24}$$

Se aplicada a transformada inversa de Fourier sobre  $H(j\omega)$  é obtido :

$$h(n) = \frac{1}{2\pi} \int_{-\pi}^{\pi} H(e^{j\omega}) \cdot e^{j\omega n} d\omega = \frac{1}{2\pi} \int_{-\pi}^{\pi} e^{-j\omega D} \cdot e^{j\omega n} d\omega, \tag{25}$$

e resolvendo a integral de (25),

$$h(n) = \frac{1}{2\pi} \left. \frac{e^{j\omega(n-D)}}{j(n-D)} \right|_{-\pi}^{\pi} = \frac{1}{2\pi} \frac{e^{j\pi(n-D)} - e^{-j\pi(n-D)}}{j(n-D)}.$$

(26)

Utilizando a fórmula de *Euler* em (26) é então obtido:

$$h(n) = \frac{sen(\pi(n-D))}{\pi(n-D)} = sinc(n-D). \tag{27}$$

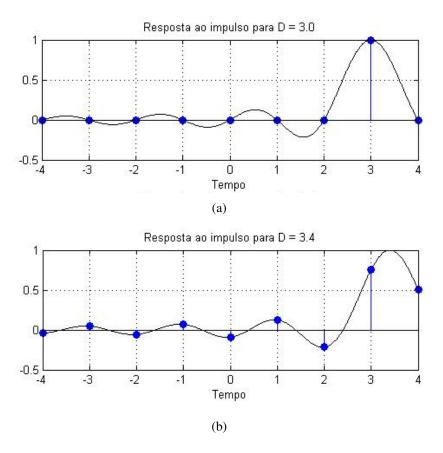

De (27) pode-se concluir que, para valores fracionários de D, o filtro ideal h(n) é não causal, já que o filtro possui infinitos valores diferentes de zero para n < 0, tornando-o irrealizável. Entretanto, para valores inteiros e positivos de D, o filtro h(n) somente é diferente de zero para n = D, justificando assim porque *delays* inteiros são causais e relativamente simples de serem implementados. A resposta ao impulso para um valor inteiro e fracionário de D é visualizada na figura 11. Na figura 11.a) pode ser visualizada a resposta ao impulso para o filtro com *delay* inteiro. Pode-se verificar nesta figura que o sinal de função sinc(n - D), considerando somente os valores inteiros de tempo, é diferente de zero somente no instante de tempo 3, valor do *delay* inteiro. A figura 11.b) apresenta a resposta ao impulso para o filtro com *delay* fracionário. Como pode ser visto na figura, nos intervalos inteiros de tempo o sinal de função sinc(n - D) sempre possui um valor diferente de zero.

Sendo o filtro ideal de *delay* fracionário não causal, somente é possível obter um filtro aproximado, contendo um erro com relação ao ideal. O filtro aproximado pode ser projetado

Figura 11: Resposta ao impulso para filtro de delay fracionário ideal com a) D=3.0 e b) D=3.4. Fonte: Autoria própria

como um filtro de estrutura FIR de ordem *N*. O projeto do filtro consiste na minimização de uma função de erro, dada por (VäLIMäKI, 1995b):

$$E(e^{j\omega}) = H_{ap}(j\omega) - H(j\omega). \tag{28}$$

Onde  $H_{ap}(j\omega)$  é a função de transferência do filtro aproximado.

# 3.1.1 PROJETO DO FILTRO PELA INTEGRAL DO MÍNIMO ERRO QUADRÁTICO

A forma mais simples de obter uma aproximação do FDF ideal é através do truncamento de sua resposta ao impulso. O truncamento também é interessante por fornecer a solução ótima para a integral de erro quadrática de  $E(e^{j\omega})$  (LAAKSO et al., 1996) (VäLIMäKI, 1995b). A integral de erro quadrática pode ser definida como:

$$E_2 = \frac{1}{\pi} \int_0^{\pi} \left| E(e^{j\omega}) \right|^2 d\omega = \frac{1}{\pi} \int_0^{\pi} \left| H_{ap}(j\omega) - H(j\omega) \right|^2 d\omega. \tag{29}$$

Utilizando o teorema de Parseval em (29):

$$E_2 = \sum_{-\infty}^{\infty} |h_{ap}(n) - h(n)|^2.$$

(30)

Considerando o truncamento da resposta impulsiva do filtro ideal por um filtro de ordem *N* pode-se escrever:

$$h_{ap}(n) = \begin{cases} sinc(n-D) & M_i \le n \le M_i + N \\ 0 & demais\ valores \end{cases}$$

(31)

A variável  $M_i$  representa o índice do primeiro valor diferente de zero na resposta ao impulso do filtro, sendo que  $M_i$  deve ser igual a zero para um filtro causal. Da equação (31) pode-se deduzir que o erro de aproximação, expresso por (30), pode ser reescrito como:

$$E_2 = \sum_{n = -\infty}^{M_i - 1} |h(n)|^2 + \sum_{n = M_i + N + 1}^{\infty} |h(n)|^2.$$

(32)

Da expressão (32) pode-se concluir que: um filtro de ordem mais elevada possui um erro menor e que, o valor da parte inteira do *delay D* deve coincidir com o centro de gravidade do filtro, próximo do valor de pico de  $h_{ap}$ . O valor da parte inteira de D é dado por (33).

$$\lfloor D \rfloor = \begin{cases} \frac{N-1}{2} & \text{se N impar} \\ \frac{N}{2} & \text{se N par} \end{cases}$$

(33)

Onde  $\lfloor D \rfloor$  denota a parte inteira do *delay D*. Apesar da simplicidade do projeto do filtro utilizando o truncamento da função sinc(n-D), os filtros obtidos desta forma geralmente não possuem resultados satisfatórios (DIAZ-CARMONA; DOLECEK, 2011). Isto é consequência do fenômeno de *Gibbs* (PROAKIS; MANOLAKIS, 1996), que causa um *ripple* na magnitude da resposta em frequência do filtro. O uso do janelamento, similar ao utilizado para amostragem de um sinal e redução de erros na FFT do sinal, pode minimizar os efeitos indesejados do fenômeno de Gibbs.

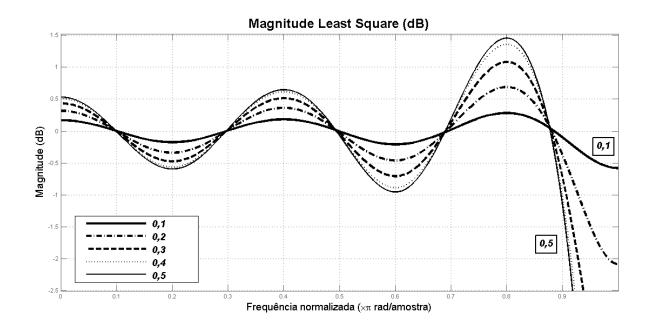

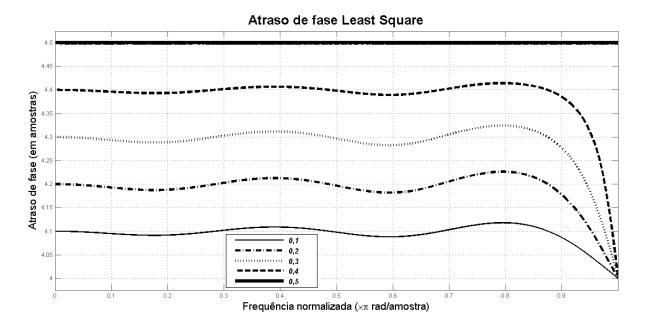

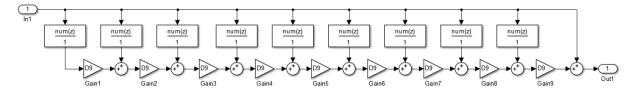

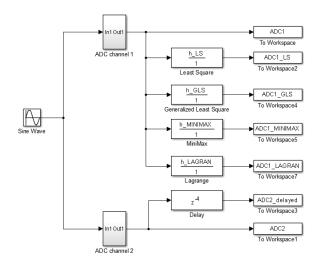

Na figura 12 é apresentada a magnitude da resposta em frequência de um filtro de ordem 9, projetado utilizando a integral do mínimo erro quadrático (ou simplesmente na sua denominação na língua inglesa *Least Square*, *LS*). Na figura 13 é apresentado o atraso de fase deste mesmo filtro. Nas duas figuras é possível observar o efeito do fenômeno de *Gibbs* sobre a resposta em frequência. Também é evidente das duas figuras que a aproximação do filtro é

mais próxima do ideal quanto menor é o valor do *delay* fracionário. Pode ser observado na figura 13 que o filtro adiciona um *delay* inteiro ao sinal de entrada. O valor deste *delay* é dado pela equação (33) para N = 9.

Figura 12: Magnitude de filtro projetado através do método *Least Square*, do *delay* 0,1 ao *delay* 0,5.

Fonte: Autoria própria

Figura 13: Atraso de fase do filtro projetado através do método Least Square, do *delay* 0,1 ao *delay* 0,5.

Fonte: Autoria própria

# 3.1.2 PROJETO DO FILTRO PELA APROXIMAÇÃO GENERALIZADA DOS MÍNIMOS QUADRADOS

Se for definida uma banda de interesse  $[0, \alpha\pi]$ , e se for aplicada uma função peso  $W(\omega) \in \Re$ + para ponderação em frequência do erro dado por (28), pode-se reescrever (29) como:

$$E_2 = \frac{1}{\pi} \int_0^{\alpha \pi} W(\omega) \left| H_{ap}(e^{j\omega}) - H(e^{j\omega}) \right|^2 d\omega. \tag{34}$$

Considere que o filtro de aproximado  $H_{ap}$  é dado por:

$$H_{ap}(e^{j\omega}) = \mathbf{h}^{\mathbf{T}}\mathbf{e}. \tag{35}$$

onde,

$$\mathbf{h} = [h(0) \ h(1) \dots h(N)]^T \mathbf{e} = \left[1 \ e^{-j\omega} \dots e^{-jN\omega}\right]^T.$$

(36)

Substituindo (35) em (34) é obtido:

$$E_{2} = \frac{1}{\pi} \int_{0}^{\alpha \pi} W(\omega) \left[ \mathbf{h}^{\mathsf{T}} \mathbf{e} - H(e^{j\omega}) \right] \left[ \mathbf{h}^{\mathsf{T}} \mathbf{e} - H(e^{j\omega}) \right]^{*} d\omega =$$

$$\frac{1}{\pi} \int_{0}^{\alpha \pi} W(\omega) \left[ \mathbf{h}^{\mathsf{T}} \mathbf{C} \mathbf{h} - 2 \mathbf{h}^{\mathsf{T}} Re \left\{ H(e^{j\omega}) \mathbf{e}^{*} \right\} + \left| H(e^{j\omega}) \right|^{2} \right] d\omega$$

(37)

Onde C é dado por:

$$\mathbf{C} = Re\left\{\mathbf{e}\mathbf{e}^{H}\right\} = \begin{bmatrix} 1 & cos(\boldsymbol{\omega}) & \dots & cos(N\boldsymbol{\omega}) \\ cos(\boldsymbol{\omega}) & 1 & \dots & cos((N-1)\boldsymbol{\omega}) \\ \vdots & \dots & & \vdots \\ cos(N\boldsymbol{\omega}) & cos((N-1)\boldsymbol{\omega}) & \dots & 1 \end{bmatrix}$$

(38)

Sendo que o sobrescrito H representa a operação Hermitiana. O erro então pode ser reescrito como:

$$E_2 = \mathbf{h}^T \mathbf{P} \mathbf{h} - 2\mathbf{h}^T \mathbf{p}_1 + p_0 \tag{39}$$

onde,

$$\mathbf{P} = \frac{1}{\pi} \int_{0}^{\alpha \pi} W(\omega) \mathbf{C} d\omega$$

$$\mathbf{p_{1}} = \frac{1}{\pi} \int_{0}^{\alpha \pi} W(\omega) \left[ ReH(e^{j\omega}) \mathbf{e} - ImH(e^{j\omega}) \mathbf{s} \right] d\omega$$

$$p_{0} = \frac{1}{\pi} \int_{0}^{\alpha \pi} W(\omega) \left| H(e^{j\omega}) \right|^{2} d\omega$$

$$\mathbf{e} = \left[ 1 \cos(\omega) \dots \cos(N\omega) \right]^{T}$$

$$\mathbf{s} = \left[ 0 \operatorname{sen}(\omega) \dots \operatorname{sen}(N\omega) \right]^{T}$$

Para encontrar o valor mínimo de erro, a solução ótima, a equação (39) é derivada em relação à **h** e igualada a zero, ou seja:

$$2\mathbf{Ph} - 2\mathbf{p_1} = 0 \tag{41}$$

A solução da equação (41) é dada formalmente pela inversão da matriz **P**, sendo obtido:

$$\mathbf{h} = \mathbf{P}^{-1}\mathbf{p}_1 \tag{42}$$

Pode-se observar que a solução ótima é obtida a partir da resolução das integrais de (40) e das (N+1) equações lineares de (42). As integrais de (40) são significativamente simplificadas quando a função ideal é dada por  $e^{-jD\omega}$  (LAAKSO et al., 1996). No caso em que a função  $W(\omega) = 1$  a solução é dada de forma fechada, sendo que  $\mathbf{P}$  e  $\mathbf{p_1}$  podem ser expressados pelas equações (43) e (44) respectivamente.

$$P_{k,l} = \frac{1}{\pi} \int_0^{\alpha \pi} \cos((k-l)\omega) d\omega = \alpha \operatorname{sinc}(\alpha(k-l)) \ k, l = 1, 2, ..., N+1$$

(43)

$$p_{1,k} = \frac{1}{\pi} \int_0^{\alpha\pi} \cos((k-D)\omega) d\omega = \alpha \operatorname{sinc}(\alpha(k-D)) \ k = 1, 2, ..., N+1$$

(44)

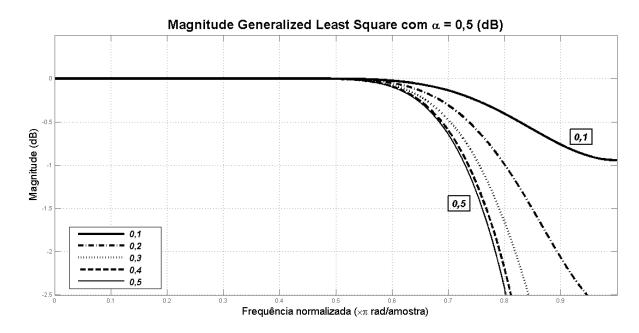

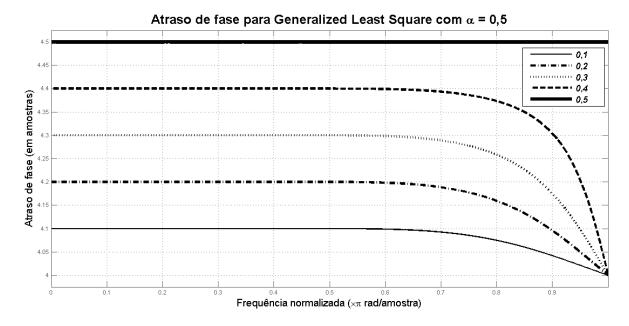

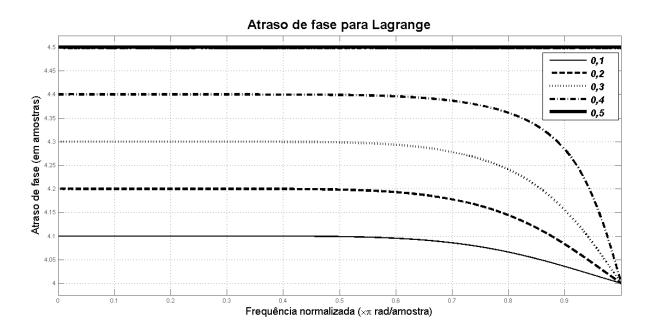

A principal vantagem do projeto pela aproximação generalizada dos mínimos quadrados (ou na sigla inglesa GLS) é a flexibidade em definir uma banda de interesse e em ponderar o erro do filtro no domínio da frequência. Ao definir uma banda de interesse e uma região em que o erro da aproximação não é importante, é possível obter um erro de aproximação menor do que no projeto de aproximação LS para um filtro de mesma ordem. Nas figuras 14 e 15 são apresentadas a magnitude e o atraso de fase, respectivamente, de filtros projetados utilizando o método GLS para  $\alpha = 0,5$ . Como pode ser observado nas duas figuras, há um

Figura 14: Magnitude de filtros projetados utilizando método GLS para  $\alpha$  = 0,5 e *delay* entre 0,1 e 0,5.

Figura 15: Atraso de fase de filtros projetados utilizando método GLS para  $\alpha$  = 0,5 e *delay* entre 0,1 e 0,5.

Fonte: Autoria própria

erro de aproximação dos filtros muito menor na banda definida por  $[0;0,5\pi]$  do que nas demais frequências.

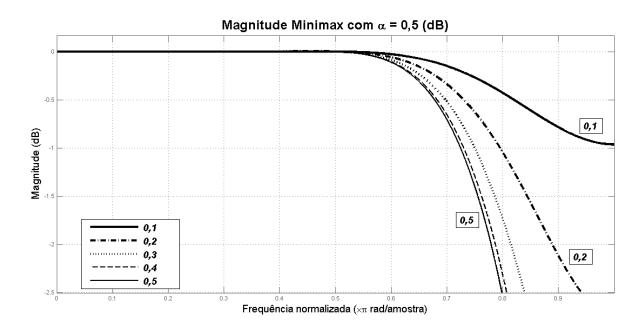

## 3.1.3 PROJETO DO FILTRO UTILIZANDO MÉTODO MINIMAX

Diferentemente dos métodos *LS* e *GLS*, o método *minimax* não busca reduzir o valor do erro quadrático da aproximação do filtro, mas sim o valor de pico do erro de aproximação, o que é expresso pela equação (45).

$$E_{max} = min\left\{max_{\omega \in [0,\alpha\pi]}\left\{\left|E(e^{j\omega})\right|\right\}\right\} \tag{45}$$

A solução para o problema da equação (45) normalmente é obtido através de métodos iterativos (VäLIMäKI, 1995b). Entretanto, em (OETKEN, 1979) é proposto um método para filtros de ordem ímpar que não requer o uso de um método iterativo. A discussão a seguir é adaptada de (VäLIMäKI, 1995b). Oetken observou que, calculando os zeros na magnitude de um único filtro ótimo (um filtro de protótipo), é possível utilizar os zeros calculados para projetar outros filtros FIR com características similares. A função de erro para um filtro de ordem N possui então K = (N+1)/2 - 1 zeros, ou seja:

$$E(e^{j\omega}) = H_{ap}(e^{j\omega}) - H(e^{j\omega}) = 0, \quad \omega = \Omega_k, \quad k = 1, 2, ..., K$$

(46)

o que implica em

$$\sum_{n=0}^{N} h(n)e^{-jn\Omega_k} = e^{-j\Omega_k \frac{N}{2}}, \quad k = 1, 2, ..., K$$

(47)

Em (47) o valor N/2 é o *delay* do filtro. A solução para os coeficientes do filtro pode ser encontrada se o valor do *delay* D for um valor próximo de N/2, o que é expresso pela equação (48).

$$\mathbf{E}_{\Omega}\mathbf{h} = \mathbf{e}_{\mathbf{D}} \tag{48}$$

Sendo  $e_D$  o vetor dado pela equação (50) e  $\mathbf{E}_{\Omega}$  a matriz de K linhas por (N+1) colunas dada por (49).

$$\mathbf{E}_{\Omega} = \begin{bmatrix} 1 & e^{-j\Omega_{1}} & e^{-j2\Omega_{1}} & \dots & e^{-jN\Omega_{1}} \\ 1 & e^{-j\Omega_{2}} & e^{-j2\Omega_{2}} & \dots & e^{-jN\Omega_{2}} \\ \vdots & \vdots & & \vdots & & \vdots \\ 1 & e^{-j\Omega_{K}} & e^{-j2\Omega_{K}} & \dots & e^{-jN\Omega_{K}} \end{bmatrix}$$

(49)

$$\mathbf{e_D} = \begin{bmatrix} e^{-jD\Omega_1} & e^{-jD\Omega_2} & \dots & e^{-jD\Omega_K} \end{bmatrix}^T$$

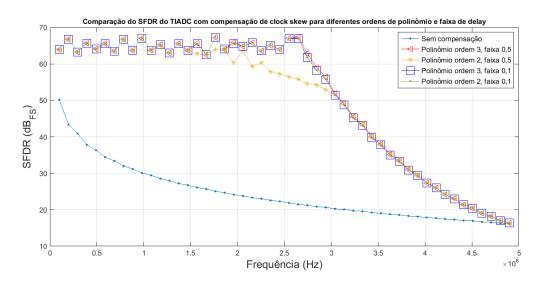

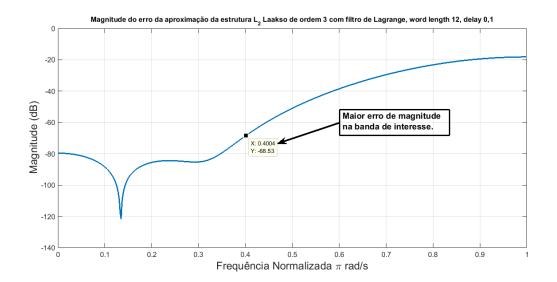

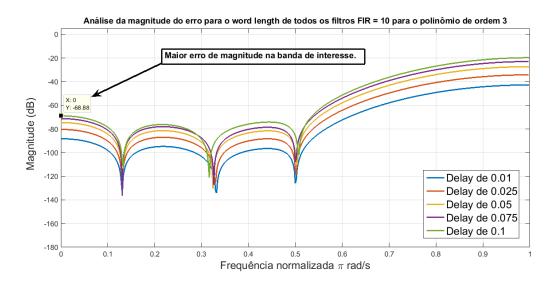

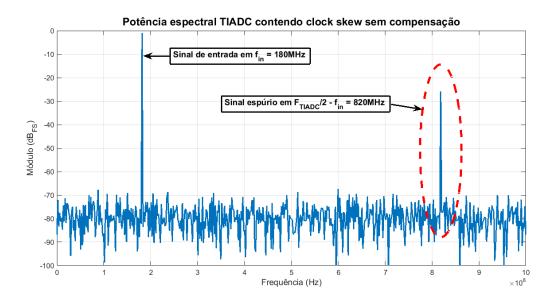

(50)