# UNIVERSIDADE TECNOLÓGICA FEDERAL DO PARANÁ DEPARTAMENTO ACADÊMICO DE ELETRÔNICA ENGENHARIA INDUSTRIAL ELÉTRICA - ÊNFASE EM ELETRÔNICA/TELECOMUNICAÇÕES

# ERIKSON FERRARINI MATEUS LUIS TONDO THIAGO SOUZA LACERDA

# PLATAFORMA DIGITAL EMULADA EM TEMPO REAL

TRABALHO DE CONCLUSÃO DE CURSO

CURITIBA 2011

# ERIKSON FERRARINI MATEUS LUIS TONDO THIAGO SOUZA LACERDA

# PLATAFORMA DIGITAL EMULADA EM TEMPO REAL

Trabalho de Conclusão de Curso apresentado ao Departamento Acadêmico de Eletrônica, como requisito parcial para a obtenção do grau de Engenheiro no curso de Engenharia Industrial Elétrica — Ênfase em Eletrônica/Telecomunicações, da Universidade Tecnológica Federal do Paraná

Orientador: Prof. Rubens Alexandre de Faria

CURITIBA 2011

#### AGRADECIMENTO

Os autores agradecem, primeiramente, aos pais e companheiras, que foram compreensivos com a abstenção de momentos da vida particular em prol da realização deste objetivo comum. Também pela orientação, confiança e apoio que ofereceram durante a longa jornada percorrida.

Agradecemos especialmente aos alunos Mikhail Koslowski, Carlos Alexandre Micaloski, Diego Dias dos Reis, Alexandre Noguchi, João Paulo Sant'anna Junior, Carlos Toledo, Philipe Ambrózio Dias e também aos professores Rubens Alexandre de Faria, Dario Dergint e Wolney Betiol que, de alguma maneira, contribuíram para o resultado deste projeto.

#### **RESUMO**

FERRARINI, Erikson; TONDO, Mateus L.; LACERDA, Thiago S.. Plataforma digital emulada em tempo real. 2011. 117 páginas. Trabalho de Conclusão de Curso – curso de Engenharia Industrial Elétrica - ênfase Eletrônica/Telecomunicações, Universidade Tecnológica Federal do Paraná, Curitiba, 2011.

Em alinhamento com as atuais metodologias de ensino, que objetivam propiciar o contato direto dos alunos com as tecnologias demandadas pelo mercado e desejáveis nos profissionais, é de fundamental importância dispor de plataformas didáticas para a familiarização com os recursos envolvidos. O objetivo principal é desenvolver uma plataforma didática microcontrolada com arquitetura de 8 bits para o auxílio na disciplina de microcontroladores da UTFPR. A metodologia envolve um estudo a ser realizado acerca do mercado nacional analisando a participação das marcas, presença de distribuidores, variedade e disponibilidade de modelos, ferramentas de desenvolvimento compatíveis e recursos disponíveis no chip. A plataforma didática desenvolvida contempla, além da placa que contém o microcontrolador de 8 bits, interfaces do tipo USB (Universal Serial Bus) para transferência de código-fonte para a placa e JTAG (Joint Test Action Group) para depuração em tempo real. Os principais resultados esperados ao final do projeto são a elevação na qualidade das disciplinas, nas quais se matriculam em torno de 130 alunos a cada semestre, através do uso de recursos mais atuais, e a transmissão de conhecimentos práticos mais alinhados com a realidade do mercado de eletrônica através do uso do kit didático.

**Palavras Chave**: *Kit* Didático. Microcontrolador 8 *bit*s. JTAG. *Debug* Tempo Real. Interface USB. Plataforma Desenvolvimento.

#### **ABSTRACT**

FERRARINI, Erikson; TONDO, Mateus L.; LACERDA, Thiago S.. **Plataforma digital emulada em tempo real.** 2011. 117 pages. End of Course Assignment – Electronic Engineering, Technological Federal University of Parana, Curitiba, 2011;

Aligned with the current teaching methodologies, which intend to promote the direct contact of students with technologies needed by the market and desirable in professionals, it is extremely important to count on didactic kits for the students to become familiar with the resources involved. The main objective is to develop a microcontrolled 8 *bits* architecture teaching platform to assist on tuition of microcontrollers' subjects at UTFPR. The methodology employed will be based on a market analysis that is going to evaluate the market share among companies, national distributors, variety and availability of models, compatible development environments and resources embedded on chip. The developed resource will contain not only the microcontrolled board, but additionally an USB interface for the source code to be transferred to the target board and a JTAG interface for real time debugging. The expected results at the end of the project are the improvement of quality on subjects (in which around 130 are enrolled every semester) by using newer resources and also promote the transmission of practical electronics knowledge by using the evaluation kit.

**Key words**: Didactic Kit, 8 bit microcontroller, JTAG, Real Time Debug, Interface USB, Evaluation Platform.

# SUMÁRIO

| 1. II   | NTRODUÇÃO                                              | 14 |

|---------|--------------------------------------------------------|----|

| 1.1.    | JUSTIFICATIVA                                          | 14 |

| 1.2.    | OBJETIVOS                                              | 15 |

| 1.2.1.  | Objetivo Geral                                         | 15 |

| 1.2.2.  | Objetivos Específicos                                  | 15 |

| 1.2.3.  | Diagrama                                               | 16 |

| 1.3.    | METODOLOGIA                                            | 16 |

| 1.4.    | APRESENTAÇÃO DO DOCUMENTO                              | 18 |

| 2. F    | UNDAMENTAÇÃO TEÓRICA                                   | 19 |

| 2.1.    | MICROCONTROLADORES                                     | 19 |

| 2.2.    | JTAG                                                   | 20 |

| 2.3.    | USB (UNIVERSAL SERIAL BUS)                             | 22 |

| 3. C    | DESENVOLVIMENTO                                        | 24 |

| 3.1.    | MICROCONTROLADORES                                     | 24 |

| 3.1.1.  | C8051F386                                              | 24 |

| 3.1.1.1 | CIP-51                                                 | 26 |

| 3.1.1.2 | Organização da memória                                 | 28 |

| 3.1.1.3 | Interrupções                                           | 30 |

| 3.1.1.4 | Oscilador e Clock                                      | 35 |

| 3.1.1.5 | Entradas e saídas                                      | 36 |

| 3.1.1.6 | Timer                                                  | 38 |

| 3.1.2.  | C8051F321                                              | 38 |

| 3.2.    | PROTOCOLO SILICON LABS C2                              | 39 |

| 3.2.1.  | Modelo de instruções                                   | 40 |

| 3.2.2.  | Ciclo de escrita de endereço (11b)                     | 42 |

| 3.2.3.  | Ciclo de leitura de endereço (10b)                     | 42 |

| 3.2.4.  | Ciclo de escrita de dados (01b)                        | 43 |

| 3.2.5.  | Ciclo de Leitura de Dados                              | 44 |

| 3.2.6.  | Considerações sobre os tempos                          | 45 |

| 3.2.7.  | Gravação da memória FLASH através do protocolo C2      | 46 |

| 3.3.7.1 | Interface C2 (C2I)                                     | 47 |

| 3.3.7.2 | Registrador de identificação do dispositivo (DEVICEID) | 47 |

| 3.3.7.3 | Registrador identificador de versão (REVID)            | 48 |

| 3.3.7.4 | Registradores para a programação da FLASH  | .49 |

|---------|--------------------------------------------|-----|

| 3.3.7.5 | Interface de programação da FLASH          | .49 |

| 3.3.7.6 | Escrita de um bloco da memória FLASH       | .49 |

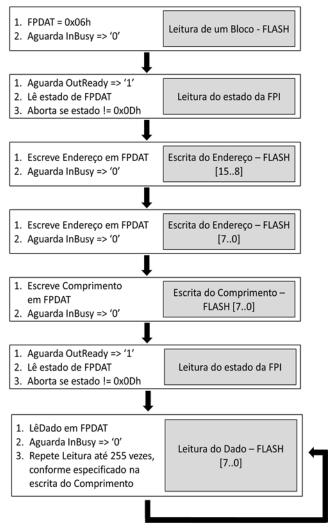

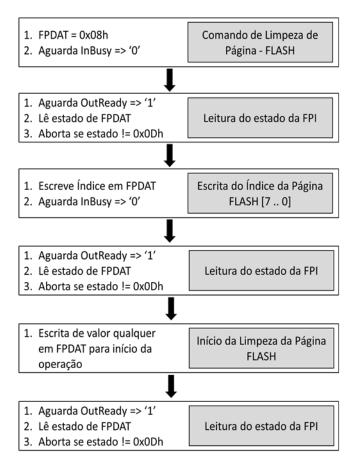

| 3.3.7.7 | Leitura de um bloco da memória FLASH       | .51 |

| 3.3.7.8 | Limpeza de uma página da memória FLASH     | .52 |

| 3.3.7.9 | Limpeza da memória FLASH completa          | .53 |

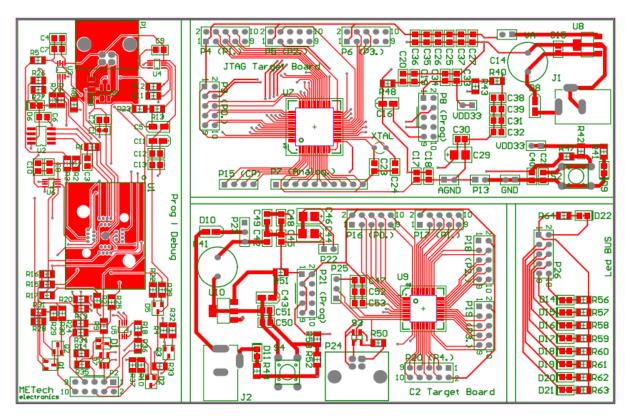

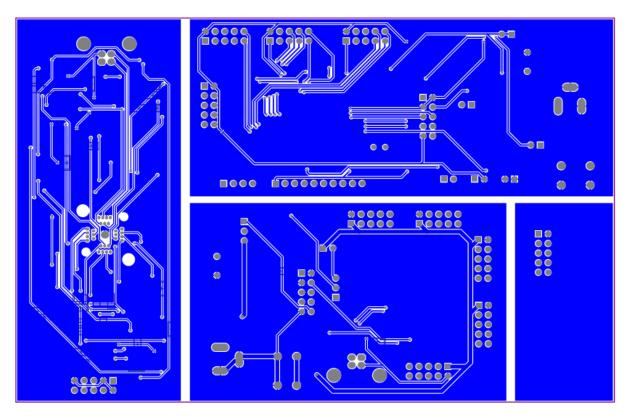

| 3.3.    | PLACAS E CIRCUITOS                         | .54 |

| 4. T    | ESTES E RESULTADOS                         | .58 |

| 4.1.    | ALIMENTAÇÃO                                | .58 |

| 4.2.    | OSCILADOR, PINOS DE ENTRADA E SAÍDA E LEDS | .59 |

| 4.3.    | DEBUG ADAPTER                              | .61 |

| 4.4.    | TESTE DO SOFTWARE C2                       | .62 |

| 4.5.    | SUGESTÕES PARA VERSÕES FUTURAS             | .63 |

| 4.6.    | CONSIDERAÇÕES                              | .63 |

| 5. C    | ONCLUSÃO TÉCNICA                           | .64 |

| 6. P    | LANO DE NEGÓCIOS                           | .66 |

| 6.1.    | SUMÁRIO EXECUTIVO                          | .66 |

| 6.1.1.  | Oportunidade de negócio                    | .66 |

| 6.1.2.  | O produto                                  | .66 |

| 6.1.3.  | A Empresa                                  | .67 |

| 6.1.4.  | Visão 2014                                 | .67 |

| 6.1.5.  | Missão                                     | .67 |

| 6.1.6.  | Valores                                    | .68 |

| 6.1.7.  | Descrição do negócio                       | .68 |

| 6.2.    | PRODUTOS E SERVIÇOS                        | .69 |

| 6.2.1.  | Características                            | .69 |

| 6.2.2.  | Produtos Similares                         | .69 |

| 6.2.3.  | Análise Comparativa                        | .71 |

| 6.2.4.  | Análise SWOT                               | .71 |

| 6.2.5.  | Produtos e serviços futuros                | .72 |

| 6.3.    | ANÁLISE DE MERCADO                         | .72 |

| 6.3.1.  | Importação de microcontroladores no Brasil | .72 |

| 6.3.2.  | Segmentação de Mercado                     | .76 |

| 6.3.3.  | Segmento Alvo de Mercado                   | .79 |

|         |                                            |     |

| 6.3.4. | Necessidades do Mercado                             | 79  |

|--------|-----------------------------------------------------|-----|

| 6.3.5. | Crescimento do Mercado                              | 81  |

| 6.3.6. | Players                                             | 83  |

| 6.3.7. | Modelo de Distribuição                              | 84  |

| 6.3.8. | Modelo de Competitividade                           | 85  |

| 6.3.9. | Proposta de valor                                   | 85  |

| 6.4.   | PLANO DE MARKETING                                  | 86  |

| 6.4.1. | Política de preços                                  | 86  |

| 6.4.2. | Estratégia de Vendas                                | 86  |

| 6.5.   | PLANO FINANCEIRO                                    | 87  |

| 6.5.1. | Investimento Inicial                                | 87  |

| 6.5.2. | Receitas                                            | 87  |

| 6.5.3. | Custos e Despesas                                   | 88  |

| 6.5.4. | Ponto de Equilíbrio                                 | 88  |

| 6.5.5. | Demonstrativo de Resultados                         | 89  |

| 6.6.   | CONSIDERAÇÕES SOBRE O PLANO DE NEGÓCIOS             | 89  |

| 7. (   | GESTÃO DE PROJETO                                   | 91  |

| 7.1.   | GERÊNCIA DO TEMPO DE PROJETO                        | 91  |

| 7.1.1. | Cronograma Planejado e Custos Homem/Hora            | 91  |

| 7.1.2. | Disparidade entre o Cronograma Previsto e Executado | 93  |

| 7.2.   | GESTÃO DE CUSTOS                                    | 93  |

| 7.3.   | GESTÃO DE RISCOS                                    | 98  |

| 7.4.   | CONSIDERAÇÕES SOBRE GESTÃO DO PROJETO               | 99  |

| 8. (   | CONCLUSÃO MERCADOLÓGICA                             | 100 |

| İ      | BIBLIOGRAFIA                                        | 101 |

| A      | ANEXOS                                              | 103 |

|        | PDETR- GUIA DO USUÁRIO                              | 109 |

# **LISTA DE FIGURAS**

| Figura 1 - Diagrama                                                 | 16 |

|---------------------------------------------------------------------|----|

| Figura 2 - Mapa de memória on-chip do C8051F38X                     | 20 |

| Figura 3 - Pinos do protocolo JTAG                                  | 21 |

| Figura 4 - Características físicas do USB                           | 22 |

| Figura 5 - Família C805138x "on chip"                               | 25 |

| Figura 6 - Diagrama de Blocos do C8051F386                          | 26 |

| Figura 7 - Diagrama de Blocos do CIP-51                             | 27 |

| Figura 8 - Mapa de memória on-chip do C8051F38                      | 28 |

| Figura 9 - Opções de osciladores                                    | 35 |

| Figura 10 - Diagrama de blocos dos pinos de entrada e saída         | 37 |

| Figura 11 - Esquemático de um pino                                  | 37 |

| Figura 12 - Diagrama de blocos da interface C2 (C2I)                | 40 |

| Figura 13 - Modelo de instruções do protocolo C2                    | 40 |

| Figura 14 - Ciclo de escrita de endereço                            | 42 |

| Figura 15 - Ciclo de leitura de endereço                            | 43 |

| Figura 16 - Ciclo de escrita de dados                               | 43 |

| Figura 17 - Ciclo de leitura de dados                               | 44 |

| Figura 18 - Diagrama de reinicialização do dispositivo alvo         | 45 |

| Figura 19 - Arquitetura da interface de programação da FLASH via C2 | 46 |

| Figura 20 - Inicialização da FPI                                    | 49 |

| Figura 21 - Escrita de um bloco da memória FLASH                    | 50 |

| Figura 22 - Leitura de um bloco da memória FLASH                    | 51 |

| Figura 23 - Limpeza de uma página da memória FLASH                  | 53 |

| Figura 24 - Limpeza da memória FLASH                                | 54 |

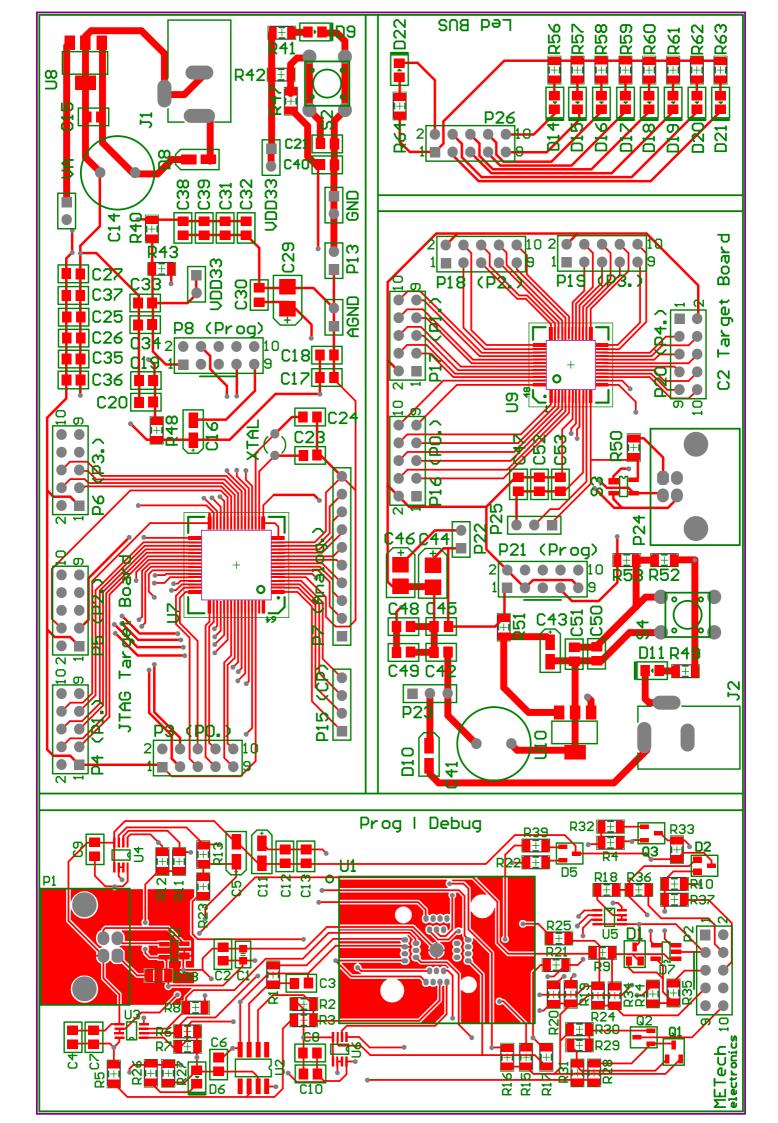

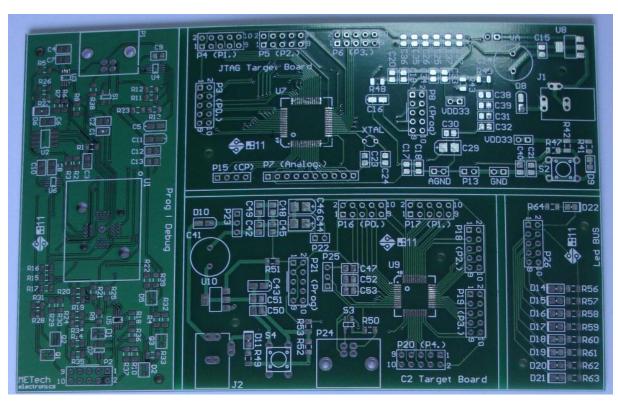

| Figura 25 - Layout da face superior da placa PDETR                  | 56 |

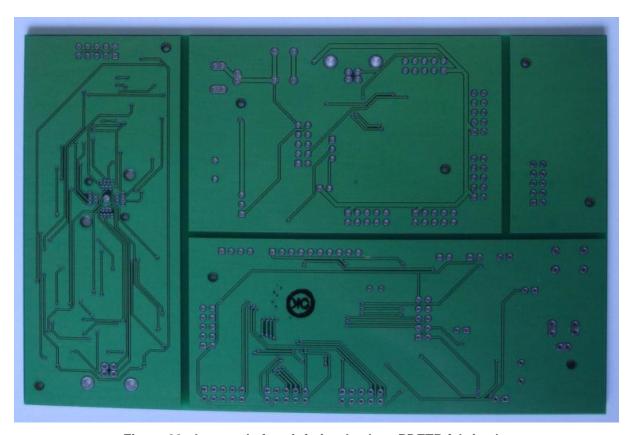

| Figura 26 - Layout da face inferior da placa PDETR                  | 56 |

| Figura 27 - Layout da face superior da placa PDETR fabricada        | 57 |

| Figura 28 - Layout da face inferior da placa PDETR fabricada        | 57 |

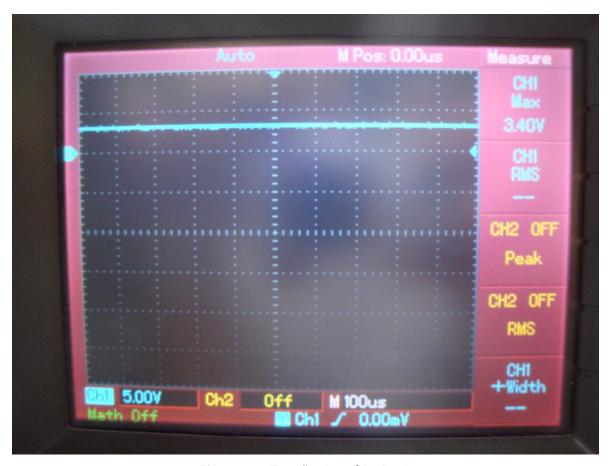

| Figura 29 - Validação do circuito de alimentação                    | 58 |

| Figura 30 - Tensão de saída da placa                                   | 59 |

|------------------------------------------------------------------------|----|

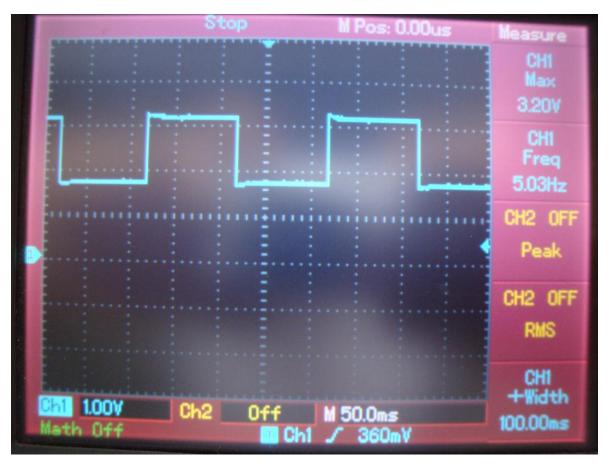

| Figura 31 - Testes de clock e pinos de saída                           | 60 |

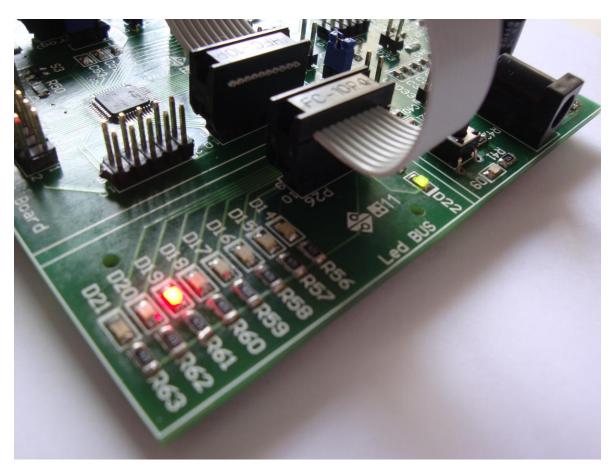

| Figura 32 - Port1 conectado ao barramento de Leds                      | 61 |

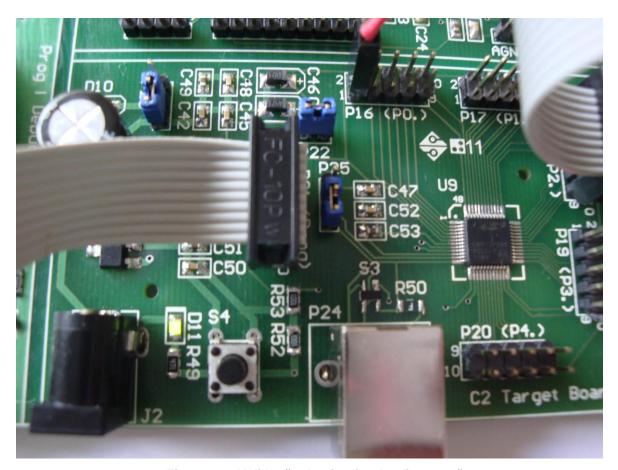

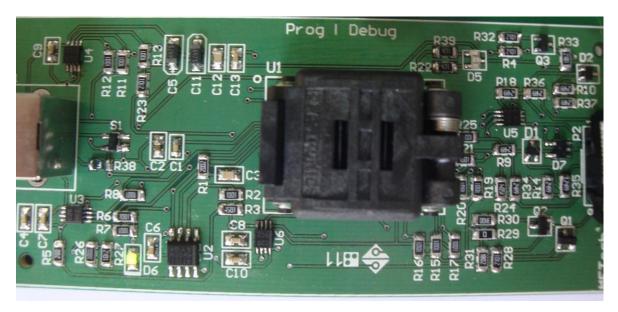

| Figura 33 - Debug Adapter conectado ao PC                              | 61 |

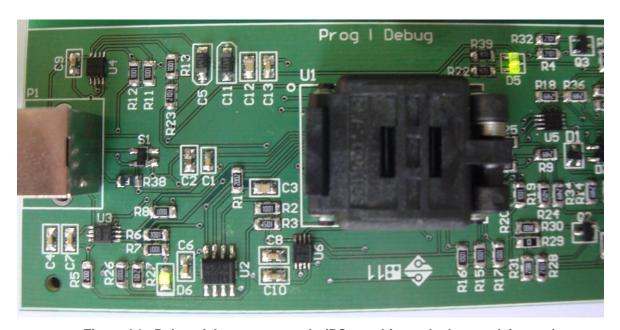

| Figura 34 - Debug Adapter conectado (PC e ambiente de desenvolvimento) | 62 |

| Figura 35 - C8051F340DK                                                | 70 |

| Figura 36 - MCB950                                                     | 70 |

|                                                                        |    |

# LISTA DE QUADROS

| Quadro 1 - Ordem de prioridade de interrupções                           | 31 |

|--------------------------------------------------------------------------|----|

| Quadro 2 – Registrador IE                                                | 32 |

| Quadro 3 – Registrador IP                                                | 33 |

| Quadro 4 – Configuração de interrupções                                  | 34 |

| Quadro 5 – Registrador IT01CF                                            | 34 |

| Quadro 6 – Registrado CLKSEL                                             | 36 |

| Quadro 7 – Distribuição dos Timers                                       | 38 |

| Quadro 8 - Instruções C2                                                 | 41 |

| Quadro 9 - Tempos limites                                                | 45 |

| Quadro 10 - Valores de retorno                                           | 47 |

| Quadro 11 - Valores de estado                                            | 48 |

| Quadro 12 - Valores configuráveis para escrita na memória FLASH          | 50 |

| Quadro 13 - Páginas da memória FLASH                                     | 52 |

| Quadro 14 - Análise comparativa                                          | 71 |

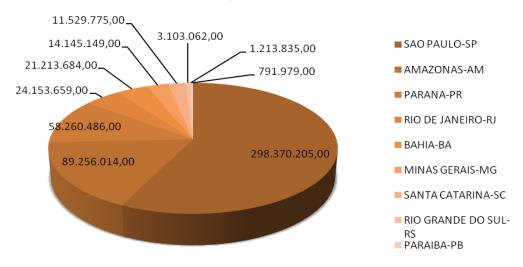

| Quadro 15 - Importações por estado brasileiro - 10 maiores               | 74 |

| Quadro 16 - Importações no Brasil – Consolidado                          | 75 |

| Quadro 17 - Segmentação de clientes potenciais                           | 77 |

| Quadro 18 - Perfil dos Egressos na Educação Superior Brasil: 2000 e 2008 | 77 |

| Quadro 19 - Concluintes da Educação Superior em Engenharia: 1999 a 2008  | 78 |

| Quadro 20 - Clientes Potenciais                                          | 79 |

| Quadro 21 - Faturamento Total por Área                                   | 82 |

| Quadro 22 - Ranking dos maiores players do mundo                         | 84 |

| Quadro 23 - Quadro de responsabilidades e ações                          | 92 |

| Quadro 24 - Lista de riscos                                              | 99 |

# LISTA DE TABELAS

| Tabela 1 - Número de instruções x Ciclos de Clock    | 27 |

|------------------------------------------------------|----|

| Tabela 2 - Investimento Inicial                      | 87 |

| Tabela 3 - Unidades produzidas X Custo de Produção   | 88 |

| Tabela 4 - Custos Fixos                              | 88 |

| Tabela 5 - Ponto de Equilíbrio                       | 89 |

| Tabela 6 - Demonstrativo de Resultados               | 89 |

| Tabela 7 - Lista de componentes para a placa alvo    | 94 |

| Tabela 8 - Lista de componentes para Debbuger        | 94 |

| Tabela 9 - Lista de componentes para pesquisa        | 95 |

| Tabela 10 - Custos com impostos                      | 95 |

| Tabela 11 - Custo de Produção para 50 PDETR          | 96 |

| Tabela 12 - Custo para produção de 50 Debug Adapters | 97 |

# LISTA DE GRÁFICOS

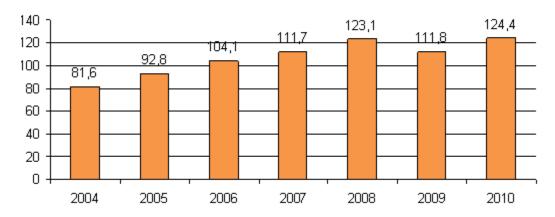

| Gráfico 1 – Importação de Microcontroladores e Microprocessadores - | Totais em |

|---------------------------------------------------------------------|-----------|

| USD                                                                 | 75        |

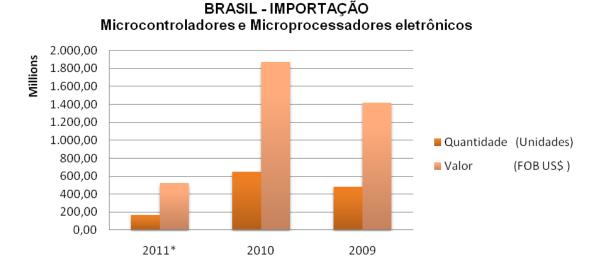

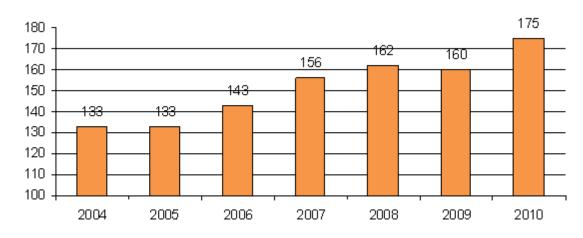

| Gráfico 2 - Importações no Brasil consolidado                       | 76        |

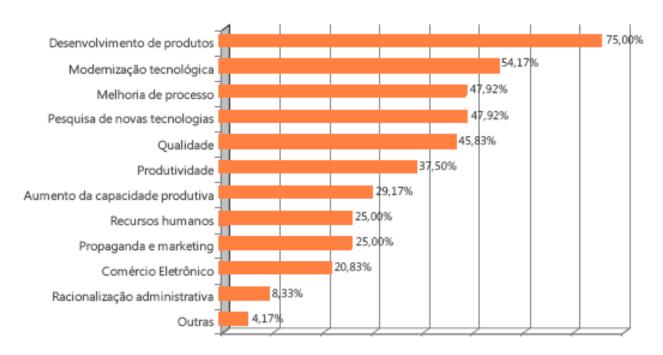

| Gráfico 3 - Investimentos no setor eletroeletrônico                 | 80        |

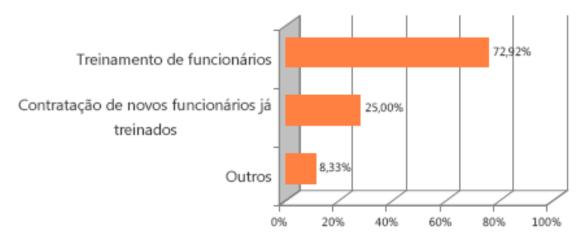

| Gráfico 4 - Treinamento de funcionários                             | 81        |

| Gráfico 5 - Faturamento Setor Eletroeletrônico                      | 82        |

| Gráfico 6 - Número de empregos formais                              | 83        |

# 1. INTRODUÇÃO

A crescente busca por profissionais mais qualificados prova a necessidade da constante melhoria e atualização do sistema de educação, como um todo, para que essa demanda seja suprida. Neste processo de melhoria contínua, deve haver investimentos na qualificação do corpo docente, passando pela estrutura física e também pelos recursos de ensino, tudo para que sejam garantidas as condições que potencializem o aprendizado do aluno no ambiente de ensino.

#### 1.1. JUSTIFICATIVA

A etapa que consiste na formação acadêmica se torna cada vez mais importante diante do refinamento das habilidades e capacidades exigidas dos profissionais que desejam se manter no mercado de trabalho. Desta forma, faz-se necessário estar alinhado com as tendências da tecnologia constantemente e, por esse motivo, é fundamental a melhoria dos recursos utilizados para treinamentos e capacitação.

Sob esta ótica, foi percebida a demanda para atualização da plataforma didática de microcontroladores utilizada na UTFPR. A evidência mais notável surgiu da observação dos computadores pessoais disponíveis no mercado. O aspecto que chamou, de fato, a atenção foi o de que o kit didático atual, utilizado em disciplinas de microcontroladores, tem como padrão de comunicação de dados para depuração e carregamento de programas a interface RS232, estabelecida em 1969(EIA STANDARD RS-232-C)<sup>9</sup>. Embora ainda utilizada, tal interface vem sendo substituída há algum tempo pelo protocolo de comunicação USB (*Universal Serial Bus*), em desenvolvimento desde 1994 (UNIVERSAL SERIAL BUS SPECIFICATION)<sup>10</sup>. Além disso, a interface RS232 é raramente encontrada nos computadores pessoais à venda e revela-se uma limitadora para o uso desta plataforma didática em um futuro próximo. Entre as vantagens do protocolo USB pode-se destacar, ainda, a maior velocidade de comunicação de dados, maior compatibilidade com periféricos e *softwares*.

Outros pontos de argumentação para ainda não haver um *kit* com conectividade USB não implementada eram os custos superiores de um microcontrolador com esta funcionalidade padronizada no *chip*, não mais um obstáculo graças à popularização desta interface, e a falta de recursos de depuração acessíveis (JTAG - *Joint Test ActionGroup*), comercializados no mercado por valores na faixa de alguns milhares de dólares, que são recursos contemplados pelo escopo do presente projeto.

Sendo assim, o *kit* renovado vai ao encontro das necessidades atuais tanto dos professores quanto dos 130 novos alunos que cursam as disciplinas de microcontroladores a cada semestre, no sentido de buscar uma alternativa de baixo custo para elevar a qualidade do ensino e potencializar a transmissão de novas tecnologias aos discentes.

Por estas razões, o fator inovador da plataforma didática que irá substituir a existente justifica a realização deste projeto.

# 1.2. OBJETIVOS

# 1.2.1. Objetivo Geral

Desenvolver uma plataforma didática microcontrolada com arquitetura de 8 bits para o auxílio na disciplina de microcontroladores da UTFPR.

### 1.2.2. Objetivos Específicos

- Desenvolver uma placa com microcontrolador de 8 bits programável em assembly no padrão CISC (ComplexInstruction Set Computer);

- Desenvolver uma interface de comunicação USB entre o PC e a placa do microcontrolador para transferência de código-fonte;

- Desenvolver hardware e firmware de uma interface de comunicação JTAG entre o PC e a placa do microcontrolador para depuração em tempo real;

Desenvolver um manual de instruções da plataforma que contemple as características técnicas da placa microcontrolada, o *layout* do hardware e os procedimentos básicos de inicialização e utilização.

# 1.2.3. Diagrama em blocos

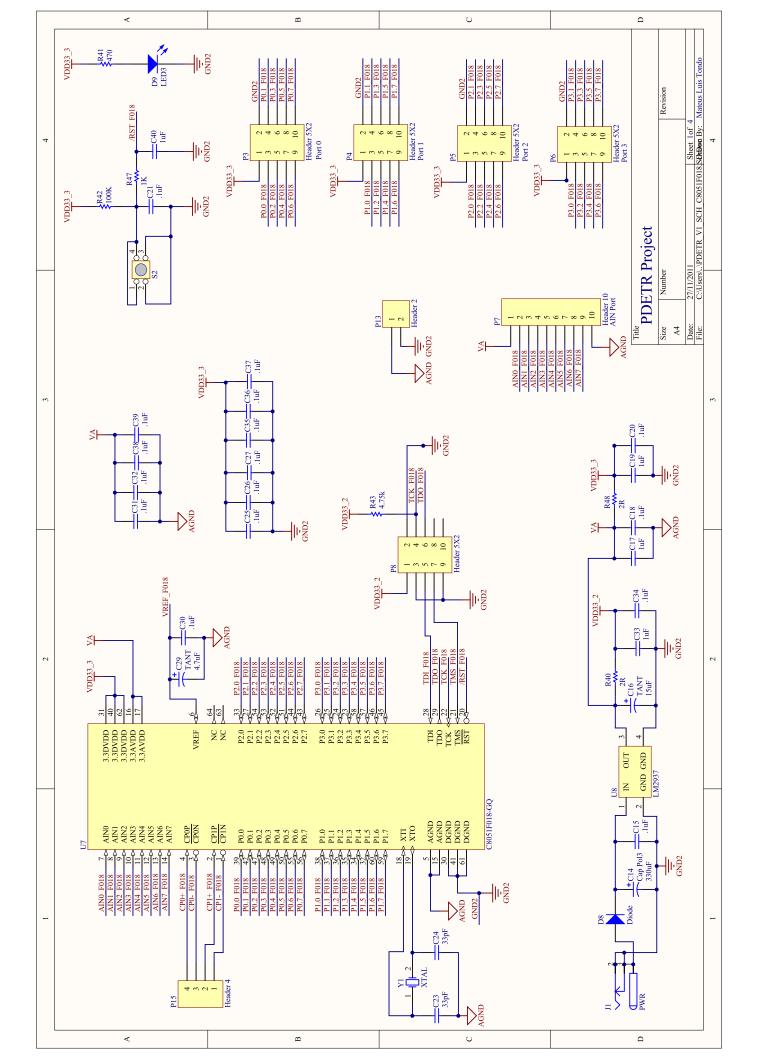

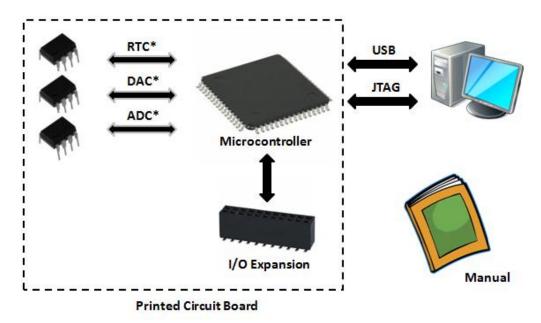

O diagrama da Figura 1 apresenta a visão do geral do projeto.

Figura 1- Diagrama Fonte: Autoria própria

### 1.3. METODOLOGIA

Para o desenvolvimento do projeto serão necessários alguns passos listados a seguir. Vale reforçar que dividiremos o tópico metodologia em três etapas:

# Etapa 1

- Estudar o mercado de microcontroladores e a participação dos fabricantes no cenário nacional;

- Estudar e definir os principais canais de distribuição dos fabricantes em questão;

- Pesquisar e definir, dentre os fabricantes mais participativos, o microcontrolador que atenda as especificações técnicas de projeto;

- Estudar a estrutura (hardware, linguagem de programação e ambiente de desenvolvimento) do microcontrolador selecionado;

A etapa 1 é considerada um ponto crítica de alto impacto para o projeto porque o microntrolador a ser utilizado na plataforma didática será selecionado a partir dos resultados obtidos nos estudos realizados.

# Etapa 2

- Desenvolver, implementar e testar circuitos e periféricos ligados ao funcionamento do microcontrolador (fonte, memória, clock e barramentos de entrada e saída);

- Pesquisar e estudar as alternativas para implementação da interface JTAG a ser utilizada para depuração em tempo real;

- Desenvolver, implementar e testar a interface JTAG;

- Integrar interfaces JTAG e USB com o microcontrolador;

- Rotear placa de circuito impresso da plataforma de desenvolvimento;

A etapa 2 é considerada um ponto crítico porque o êxito no desenvolvimento e implementação da solução proposta, com base nas tecnologias selecionadas, está diretamente ligada aos objetivos definidos no projeto.

# Etapa 3

Comprar componentes eletrônicos para montagem da placa de circuito impresso;

- Fabricar a placa de circuito impresso da plataforma;

- Montar e testar a placa de circuito impresso;

- Desenvolver atividades para demonstração da plataforma em funcionamento;

- Redigir o manual de instruções;

# 1.4. APRESENTAÇÃO DO DOCUMENTO

Pretende-se com esse documento descrever o processo de desenvolvimento do projeto final dos alunos Erikson Ferrarini, Mateus Luis Tondo e Thiago Souza Lacerda do curso de Engenharia Elétrica – Ênfase em Eletrônica/Telecomunicações da Universidade Tecnológica Federal do Paraná.

Primeiramente é discutida a metodologia utilizada para desenvolver o projeto. A seguir, é feita uma descrição das tecnologias utilizadas e das etapas executadas no desenvolvimento do projeto. Posteriormente, em Testes e Resultados, é apresentada a situação atual do projeto e as sugestões para as mudanças em relação ao que foi inicialmente planejado.

Na sequência, é descrito o plano de negócios, contendo informações sobre o produto, mercado, análise de marketing e questões financeiras. Por fim, apresentase a Gestão do Projeto e uma conclusão a respeito das etapas de desenvolvimento e do resultado final obtido. Em anexo, encontram-se o manual do produto e esquemáticos.

# 2. FUNDAMENTAÇÃO TEÓRICA

Faz-se necessário, antes de realizar a abordagem dos aspectos referentes ao desenvolvimento do projeto, uma breve fundamentação a respeito das tecnologias, dispositivos e conceitos associados. Busca-se, assim, alcançar uma contextualização adequada e facilitar a compreensão do escopo contemplado. Neste capitulo será feita uma breve descrição sobre microcontroladores 8051, protocolo JTAG e interface USB.

#### 2.1. MICROCONTROLADORES

Os microcontoladores são componentes eletrônicos concebidos para realizar a função de controle em sistemas, substituindo componentes eletromecânicos usados outrora em diversos produtos utilizados no cotidiano. Desenvolvidos com base nos conceitos da eletrônica digital, estes dispositivos são marcados por duas características fundamentais: a capacidade de serem programados para operar dados sem a intervenção humana e a capacidade de armazenar e trocar dados com outros elementos de um sistema.

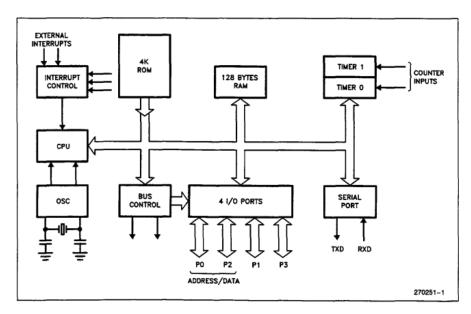

Na década de 80 os primeiros modelos de microcontroladores foram lançados, e exatamente no ano de 1980 a fabricante Intel lançou o 8051(MACKENZIE. I. SCOTT)<sup>13</sup>. Este foi o primeiro modelo produzido no padrão da família MCS-51, uma arquitetura desenvolvida pela Intel, com registradores e barramento de dados de 8 *bits* – e por esse motivo dito um microcontrolador de 8 *bits*. Esta linha era integrada por mais de 60.000 transistores, 4*kbytes* de memória de programa (ROM), 128 *bytes* de memória de dados (RAM), 32 pinos de entrada/saída, porta serial, interrupções, dois temporizadores de 16 *bits* e circuito gerador de *clock* integrado MCS 51 (MICROCONTROLLER FAMILY USER'S MANUAL)<sup>11</sup>, sendo estas características avançadas para um único circuito integrado naquela época. O diagrama em blocos do MCS-51 pode ser visto na Figura 2.

O funcionamento dos microcontroladores se dá pela realização de operações aritméticas (Adição, Subtração, Divisão e Multiplicação), lógicas (AND, OR, NOT, etc), manipulação de dados e operações de salto, todas representadas por códigos binários, chamados de grupo de instruções, operadas pela Unidade

Central de Processamento (CPU), que no caso de uma aplicação se encontram programadas internamente à memória de programa.

Figura 2- Mapa de memória on-chip do C8051F38X Fonte: (INTEL, 1994)

O grupo de instruções que leva o mesmo nome da família de *chips* MCS-51 é otimizado para trabalhar com 8 *bits* e provê uma variedade de formas de acesso à memória para facilitar as operações de *bytes* e manipulações de *bits* individualmente em sistemas de controle e lógica que demandam processamento Booleano. Através deste grupo de instruções é possível realizar a operação do núcleo do controlador e viabilizar a sua interação com os outros blocos do componente, criando uma interface com o ambiente externo à pastilha.

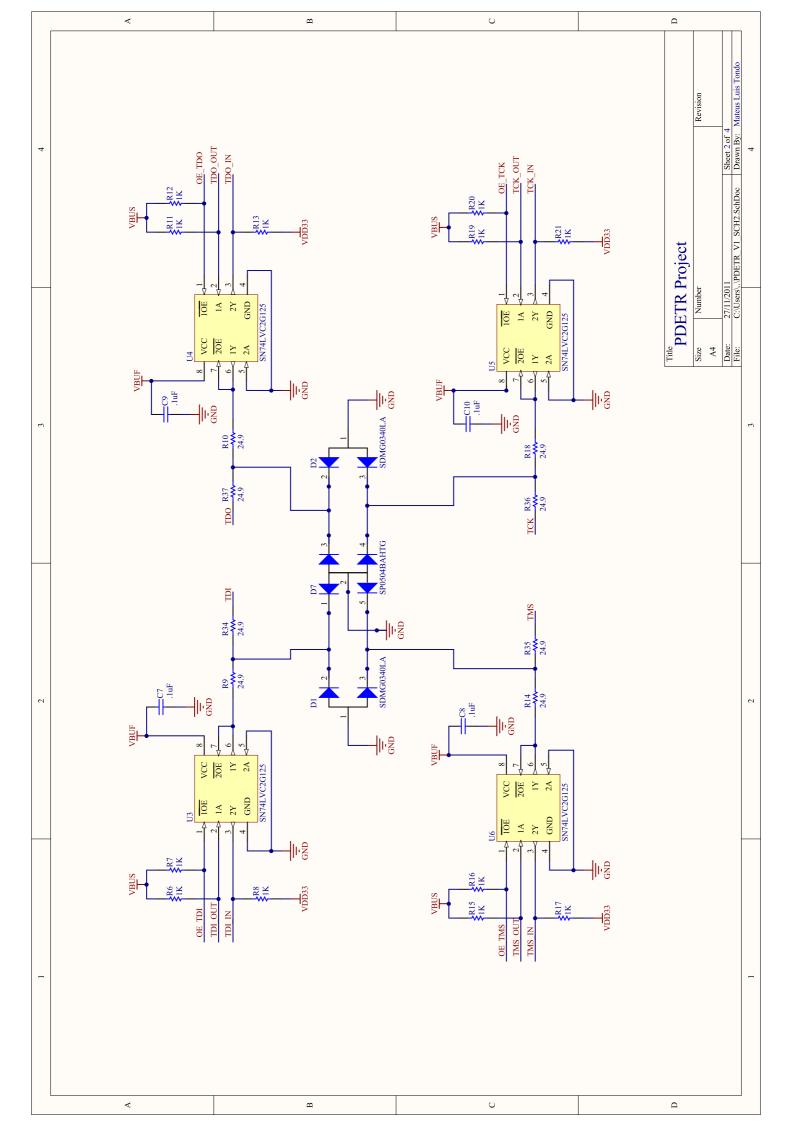

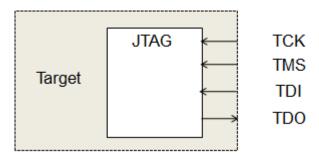

# 2.2. JTAG (Joint Test Action Group)

Em 1985, um grupo de empresas europeias de sistemas eletrônicos formou o *Joint European Test Action Group* (JETAG), com o objetivo de padronizar um método de testes de circuito impresso(IEEE STD 1149.1 (JTAG) TESTABILITYPRIMER)<sup>12</sup>. Em 1988, com a entrada da América do Norte, o grupo mudou para JTAG e em 1990 o IEEE padronizou o conceito e criou a norma 1149.1 conhecida como:

IEEE Standard Test Access Port and Boundary Scan Architecture

Inicialmente o protocolo JTAG foi usado para testes de *chips* e placas através do método *Boundary Scan*. Hoje ele é utilizado para depuração em tempo real e gravação de código e dados em memórias FLASH, além de estar presente nos principais microprocessadores utilizados pela indústria eletrônica atual.

Como características físicas ele apresenta uma arquitetura de quatro fios. Um para *clock*, dois para envio e recebimento de dados e informações e um fio de controle (Figura 3). Um pino adicional de *reset* pode ser utilizado se necessário.

Figura 3 - Pinos do protocolo JTAG Fonte: Autoria própria

O TCK (*Test clock*) é um pino de controle que recebe um sinal de *clock* independente do *clock* do sistema. A frequência de TCK deve ser suportada pelo circuito com o qual se deseja trocar informações. O TDI (*Test Data Input*) recebe serialmente os dados e instruções de entrada sempre na borda de subida do TCK. O TMS (*Test Mode Select*) é um pino de controle utilizado para se orientar através dos estados da máquina de estados do protocolo. O TDO (*Test Data Output*) entrega serialmente os dados de saída sempre na borda de descida do TCK. O TAP (*Test Access Port*) é uma máquina de estados finita que responde por variações nos sinais TCK e TMS e controla os estados do circuito de teste. As transições de estado ocorrem baseadas no valor de TMS durante a borda de subida do TCK, ou quando ocorrer um *reset* (O TRST é um pino de reset opcional do protocolo). O TAP deve gerar os sinais para controlar a operação dos circuitos envolvidos no teste.

A utilização do protocolo JTAG foi indicada na proposta do PDETR, porém, durante o desenvolvimento do projeto, julgou-se necessário sua substituição. O protocolo C2 da *Silicon Labs*, similar ao IEEE 1149.1, foi adotado e será descrito neste relatório.

# 2.3. USB (Universal Serial Bus)

A interface USB surgiu originalmente como um esforço em conjunto de sete empresas (COMPAQ, INTEL, MICROSOFT, HP, LUCENT, DEC e PHILIPS) que tinham como objetivo padronizar uma comunicação entre o computador pessoal e seus periféricos. O trabalho de normatização e organização da documentação foi posteriormente repassado para uma organização independente, o USB-IF (USB *Implementation Forum*) (UNIVERSAL SERIAL BUS SPECIFICATION)<sup>10</sup>. De 1996 até 2011, foram lançadas cinco versões do protocolo USB. Em 1996 surgiu a Versão 1.0 que suportava as funções *Low Speed* (1,5 Mb/s) e *Full Speed* (12 Mb/s). Em 1998 a versão 1.1 adicionou melhorias e, principalmente, fez esclarecimentos sobre o protocolo. A função *High Speed* (480 Mb/s) foi introduzida junto com a versão 2.0 em 2000. Em 2001 surgiu a versão USB OTG que permite aos periféricos atuarem como *hosts* (mestres) e em 2008 a versão foi lançada com suporte a 4 Gb/s (UNIVERSAL SERIAL BUS SPECIFICATION)<sup>10</sup>.

As principais características do USB são o baixo custo, utilizar um único padrão de conectores e cabos, permitir a alimentação do periférico a partir do barramento (*Bus Powered Devices*), permitir a conexão com o sistema energizado (*Hot Pluggable*), suporte para reconhecimento automático de dispositivos (*Plug and Play*), previsão para mecanismos de detecção e correção de erros (*Handshaking*), previsão de mecanismos para conservação de energia (*Power Down*) (UNIVERSAL SERIAL BUS SPECIFICATION)<sup>10</sup>.

V<sub>u</sub>

D+

Par para sinalização Diferencial

GND

Fisicamente a conexão USB é implementada através de 4 fios (Figura 4).

Figura 4 Características físicas do USB

Fonte: Autoria própria

Quanto à comunicação entre dispositivos USB, existem três classes disponíveis: Communication Device Class (CDC), Communication Interface Class (CIC) e Data Interface Class (DIC). A Communication Device Class é uma definição de nível de dispositivo e é usada pelo host para identificar corretamente um dispositivo de comunicação que pode apresentar diferentes tipos de interface. Ela fornece uma classe de dispositivo único, porém pode haver mais de uma interface implementada (interfaces de controle, dados, áudio e armazenamento em massa). A CDC define um mecanismo de propósito geral que pode ser usado para habilitar todos os tipos de serviços de comunicação no USB. A DIC define um mecanismo de propósito geral para permitir a transferência de dados. Ela identifica as interfaces de transmissão de dados quando os dados não coincidem com a estrutura ou modelo de utilização para qualquer outro tipo de classe(UNIVERSAL SERIAL BUS SPECIFICATION)<sup>10</sup>.

#### 3. DESENVOLVIMENTO

Os módulos elaborados durante o desenvolvimento do projeto serão apresentados neste capítulo. Inicialmente as características principais dos microcontroladores selecionados serão descritas com detalhes, uma vez que o conhecimento aprofundado do microcontrolador selecionado faz parte do desenvolvimento da PDETR. Na sequência será apresentado o protocolo de depuração em tempo real e suas funções utilizadas para gravar conteúdos na memória flash dos dispositivos alvos. Por fim, será apresentado o projeto das placas desenvolvidas e fabricadas.

### 3.1. MICROCONTROLADORES

Frente ao grande número de fabricantes e famílias de controladores com arquitetura 8051, fez-se uma pesquisa de mercado com o objetivo de selecionar um modelo de controlador que atendesse, o mais próximo possível, as características propostas no projeto da PDETR. Levando em consideração as características técnicas do componente e sua representação de sua fabricante no mercado nacional, os microcontroladores selecionados para a placa didática e para o dispositivo de gravação foram, respectivamente, o C8051386 e o C8051321, ambos da fabricante *Silicon Labs*.

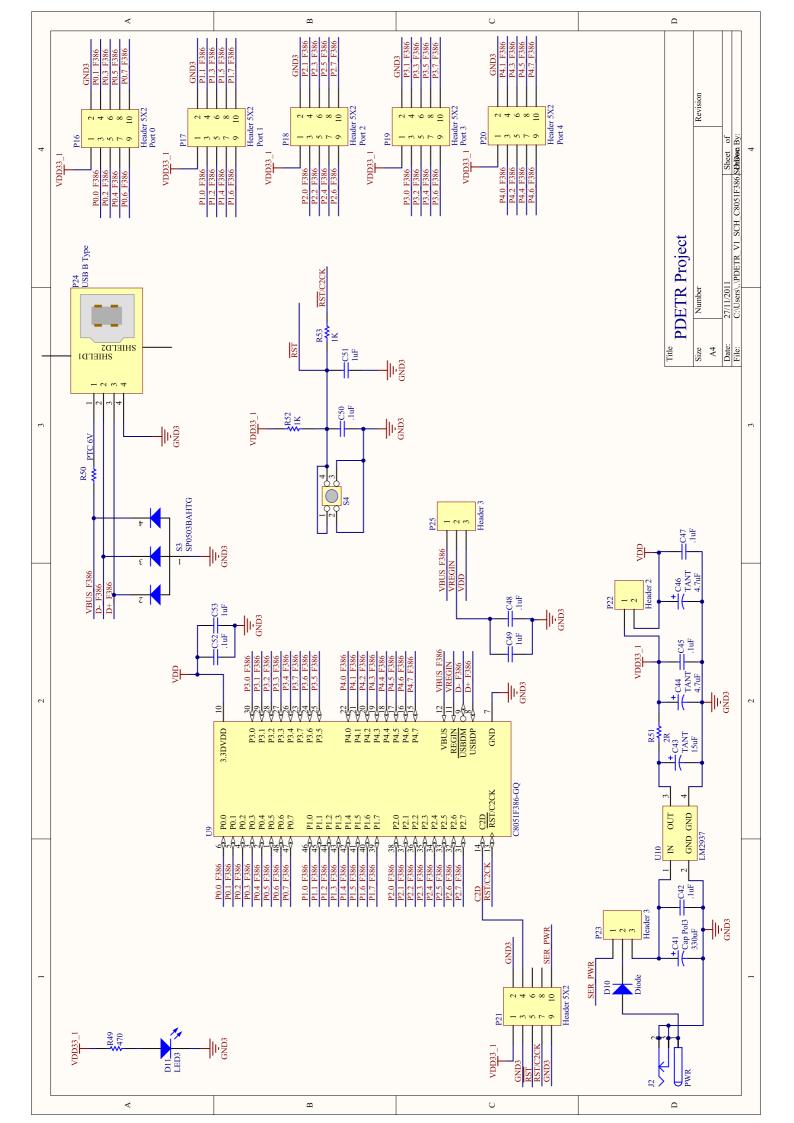

### 3.1.1. C8051F386

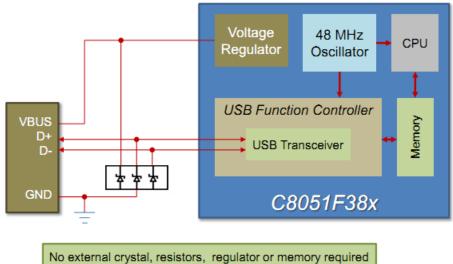

O microcontrolador C8051F386 é um controlador de 8 *bit*s da família C8051F38x desenvolvido pela *Silicon Labs*. Ele se enquadra na proposta inicial por ser um dispositivo de arquitetura 8051, com interfaces C2 e USB, que possui todas as suas atribuições e periféricos *on-chip*. Isto significa dizer que osciladores, resistores, reguladores de tensão, controlador e *transceiver* USB e memória programável estão integrados no mesmo *chip* conforme ilustra a Figura 5.

Figura 5 - Família C805138x "on chip" Fonte: (Silicon Labs, 2011)

As principais características do C8051F386 são (C8051F380/1/2/3/4/5/6/7. MANUAL. SILICON LABS)14:

- Arquitetura 8051;

- Programável em assembly por instruções CIP-51, equivalentes ao padrão MCS-51 desenvolvido pela Intel;

- Oscilador interno de frequência 48 MHz;

- Memória FLASH de 32 kbytes;

- Memória RAM 2304 bytes;

- Interface USB;

- Regulador de Tensão interno com saída 3.3 V;

- Duas interfaces SMBus/I2C (System Management Bus/Inter-Integrated Circuit);

- Interface SPI (Serial Peripheral Interface);

- Duas interfaces UART (*Universal Asynchrounous Receiver/Transmitter*);

- Seis temporizadores (*Timers* de 16 *bits*);

- PCA (Programmable Counter/Timer Array) com 5 modos de captura Watchdog Timer;

- Quatro ports de Entrada/Saída (totalizando 40 pinos de e/s);

- Interface para memória externa;

- Dois comparadores analógicos;

Interface de programação da memória FLASH (C2);

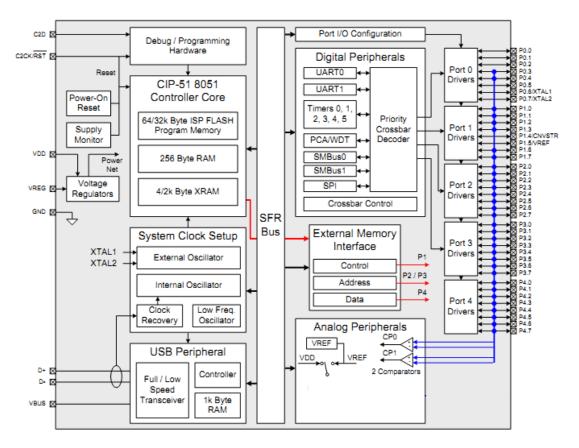

A Figura 6 mostra o diagrama de blocos de todos os módulos do C8051F386 e como os mesmos se relacionam.

Figura 6 - Diagrama de Blocos do C8051F386 Fonte: (Silicon Labs, 2011)

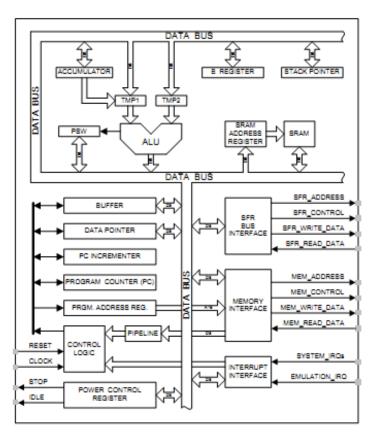

#### 3.1.1.1 CIP-51

O núcleo do C8051F386 é o CIP-51, arquitetura patenteada e pertencente à *Silicon Labs*(Figura 7). Implementado em arquitetura padrão 8051, ele é totalmente compatível com o conjunto de instruções MCS-51™ e assembladores e compiladores 803x/805x(C8051F380/1/2/3/4/5/6/7. MANUAL. SILICON LABS)<sup>14</sup>. Diferente dos microcontroladores 8051 convencionais, o core CIP-51 utiliza o sistema *pipeline* para processar instruções, o que o torna mais rápido e eficiente. Um microcontrolador 8051 comum possui um *clock* de sistema de 12MHz e processa a maioria de suas instruções (exceção MUL e DIV) com 12 ou 24 ciclos de

*clock*. O núcleo CIP-51 executa 70% de suas instruções com um ou dois ciclos de *clock* em até 48MHz.

Figura 7 - Diagrama de Blocos do CIP-51 Fonte: (Silicon Labs, 2011)

.

O CIP-51 possui 109 instruções. A Tabela 1 mostra o numero de instruções que necessitam uma quantidade conhecida de ciclos de *clock* para serem executadas.

Tabela 1 - Número de instruções x Ciclos de Clock

| Ciclos de clock | 1  | 2  | 2/4 | 3  | 3/5 | 4 | 5 | 4/6 | 6 | 8 |

|-----------------|----|----|-----|----|-----|---|---|-----|---|---|

| N°de instruções | 26 | 50 | 5   | 10 | 6   | 5 | 2 | 2   | 2 | 1 |

Fonte: (Silicon Labs, 2011)

O CIP-51 pode ser programado e depurado pela interface C2 da Silicon Labs. Esta interface, que será apresentada neste relatório, permite durante a

depuração a realização de configurações de hardware, inserir pontos de interrupção, iniciar interrupções, ler e escrever na memória, tudo sem utilizar recursos do *chip*, como o *timer* por exemplo. O *core* em questão é suportado pelo ambiente de desenvolvimento do fabricante e de terceiros.

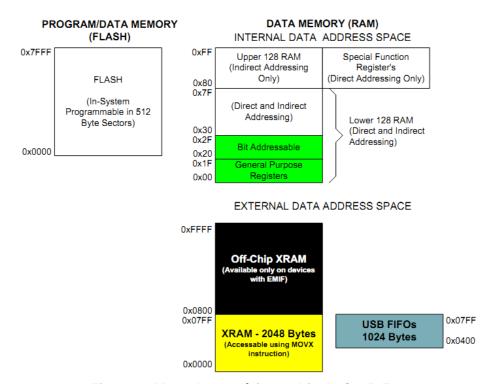

# 3.1.1.2 Organização da memória

A organização da memória do controlador CIP-51 é semelhante a um 8051 convencional. Há dois espaços de memória diferentes: memória de programa e memória de dados. As duas compartilham o mesmo espaço de endereço, mas são acessadas através de diferentes tipos de instruções. A disposição da memória do CIP-51 é mostrada na Figura 8.

Figura 8 - Mapa de memória on-chip do C8051F38 Fonte: (Silicon Labs)

# Memória de programa

O CIP-51 possui 32k*bytes* de memória de programa do tipo FLASH. Normalmente esta memória é apenas para leitura (*read-only*), porém o CIP51 pode escrever na memória de programa usando o *Program Store Write Enable bit* (PSCTL.0) associado à instrução MOVX. Este recurso fornece um mecanismo para a atualização do código do programa e liberação de espaço da memória de programa para utilizar como memória não volátil de armazenamento de dados.

# Memória de dados

O CIP-51 possui 256 *bytes* para memória RAM interna mapeados na memória de dados de 0x00 até 0xFF. Os primeiros 128 *bytes* da memória de dados são utilizados para registradores de propósito gerais. Os locais 0x00 até 0x1F são endereçados através de quatro banco de registradores de uso geral. Os próximos 16 *bytes*, 0x20 até 02F, podem ser tratadas como *bytes* ou128 *bits* acessíveis de modo direto.

#### Registradores de propósito geral

Os primeiros 32 *bytes* da memória de dados, localizados em 0x00 até 0x1F, podem ser tratados como 4 bancos de 8 registradores (R0 até R7). Esses bancos podem ser ativados um por vez através de 2 *bits* no registrador PSW (RS0 = PSW.3 e RS1 = PSW.4).

### Pilha

A pilha pode estar localizada em qualquer lugar da memória de dados. Sua área é indicada usando o *Stack Pointer* (SP, 0x81). O SP aponta para o ultimo valor empilhado, assim, quando inserimos um valor na pilha, o ponteiro é incrementado na sequência. Toda vez que um *reset* acontece, o SP encontra-se no endereço 0x07. A pilha pode ter um tamanho máximo de 256 *bytes*.

## Registradores de funções especiais

O local 0x80 até 0xFF da memória de dados é destinado os registradores de funções especiais. Consultar a documentação do C8051F386 para obter a lista de registradores especiais.

# 3.1.1.3 Interrupções

O C8051F386 contém um sistema de interrupção que suporta múltiplas fontes de interrupção com dois níveis de prioridade. Quando o sistema recebe uma interrupção, a *flag* referente a esta fonte de interrupção vai para valor lógico '1'. A CPU gera um LCALL para um endereço pré-determinado que tratará a interrupção. O fim dessa rotina deve terminar com RETI, que retorna a execução do programa principal para a próxima instrução que seria executada se a interrupção não tivesse ocorrido. As interrupções devem ser globalmente habilitadas no *bit* EA (*Global Interrupt Enable*) do registrador IE.

# Prioridades

Cada fonte de interrupção pode ser individualmente programada para um dos dois níveis de prioridade: alta ou baixa. A prioridade baixa é padrão. Uma rotina de tratamento de interrupção de baixa prioridade pode ser interrompida por uma interrupção de alta prioridade. Se duas interrupções definidas com o mesmo nível de prioridade acontecem simultaneamente, a ordem de atendimento de interrupção é dada segundo o Quadro 1. Cada fonte de interrupção tem um *bit* de prioridade associado nos registradores IP, EIP1 ou EIP2.

| Interrupt Source                | Interrupt<br>Vector | Priority<br>Order | Pending Flag                                                               | Bit<br>Address? |     | Enable<br>Flag     | Priority<br>Control |

|---------------------------------|---------------------|-------------------|----------------------------------------------------------------------------|-----------------|-----|--------------------|---------------------|

| Reset                           | 0x0000              | Тор               | None                                                                       | N/A             | N/A | Always<br>Enabled  | Always<br>Highest   |

| External Interrupt 0<br>(INT0)  | 0x0003              | 0                 | IE0 (TCON.1)                                                               | Y               | Υ   | EX0 (IE.0)         | PX0 (IP.0)          |

| Timer 0 Overflow                | 0x000B              | 1                 | TF0 (TCON.5)                                                               | Υ               | Υ   | ET0 (IE.1)         | PT0 (IP.1)          |

| External Interrupt 1<br>(INT1)  | 0x0013              | 2                 | IE1 (TCON.3)                                                               | Y               | Y   | EX1 (IE.2)         | PX1 (IP.2)          |

| Timer 1 Overflow                | 0x001B              | 3                 | TF1 (TCON.7)                                                               | Υ               | Υ   | ET1 (IE.3)         | PT1 (IP.3)          |

| UART0                           | 0x0023              | 4                 | RI0 (SCON0.0)<br>TI0 (SCON0.1)                                             | Y               | N   | ES0 (IE.4)         | PS0 (IP.4)          |

| Timer 2 Overflow                | 0x002B              | 5                 | TF2H (TMR2CN.7)<br>TF2L (TMR2CN.6)                                         | Y               | N   | ET2 (IE.5)         | PT2 (IP.5)          |

| SPI0                            | 0x0033              | 6                 | SPIF (SPI0CN.7)<br>WCOL (SPI0CN.6)<br>MODF (SPI0CN.5)<br>RXOVRN (SPI0CN.4) | Y               | N   | ESPIO<br>(IE.6)    | PSPI0<br>(IP.6)     |

| SMB0                            | 0x003B              | 7                 | SI (SMB0CN.0)                                                              | Y               | N   | ESMB0<br>(EIE1.0)  | PSMB0<br>(EIP1.0)   |

| USB0                            | 0x0043              | 8                 | Special                                                                    | N               | N   | EUSB0<br>(EIE1.1)  | PUSB0<br>(EIP1.1)   |

| ADC0 Window Com-<br>pare        | 0x004B              | 9                 | ADOWINT<br>(ADC0CN.3)                                                      | Y               | N   | EWADC0<br>(EIE1.2) | PWADC0<br>(EIP1.2)  |

| ADC0 Conversion<br>Complete     | 0x0053              | 10                | ADOINT (ADCOCN.5)                                                          | Y               | N   | EADC0<br>(EIE1.3)  | PADC0<br>(EIP1.3)   |

| Programmable Coun-<br>ter Array | 0x005B              | 11                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)                                           | Y               | N   | EPCA0<br>(EIE1.4)  | PPCA0<br>(EIP1.4)   |

| Comparator0                     | 0x0063              | 12                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5)                                     | N               | N   | ECP0<br>(EIE1.5)   | PCP0<br>(EIP1.5)    |

| Comparator1                     | 0x006B              | 13                | CP1FIF (CPT1CN.4)<br>CP1RIF (CPT1CN.5)                                     | N               | N   | ECP1<br>(EIE1.6)   | PCP1<br>(EIP1.6)    |

| Timer 3 Overflow                | 0x0073              | 14                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)                                         | N               | N   | ET3<br>(EIE1.7)    | PT3<br>(EIP1.7)     |

| VBUS Level                      | 0x007B              | 15                | N/A                                                                        | N/A             | N/A | EVBUS<br>(EIE2.0)  | PVBUS<br>(EIP2.0)   |

| UART1                           | 0x0083              | 16                | RI1 (SCON1.0)<br>TI1 (SCON1.1)                                             | N               | N   | ES1<br>(EIE2.1)    | PS1<br>(EIP2.1)     |

| Reserved                        | 0x008B              | 17                | N/A                                                                        | N/A             | N/A | N/A                | N/A                 |

| SMB1                            | 0x0093              | 18                | SI (SMB1CN.0)                                                              | Y               | N   | ESMB1<br>(EIE2.3)  | PSMB1<br>(EIP2.3)   |

| Timer 4 Overflow                | 0x009B              | 19                | TF4H (TMR4CN.7)<br>TF4L (TMR4CN.6)                                         | Y               | N   | ET4<br>(EIE2.4)    | PT4<br>(E!P2.4)     |

| Timer 5 Overflow                | 0x00A3              | 20                | TF5H (TMR5CN.7)<br>TF5L (TMR5CN.6)                                         | Y               | N   | ET5<br>(EIE2.5)    | PT5<br>(E!P2.5)     |

Quadro 1 - Ordem de prioridade de interrupções Fonte: (Silicon Labs, 2011)

# IE (Interrupt Enable)

O Quadro 2 decreve o registrador IE.

SFR Address = 0xA8; SFR Page = All Pages; Bit-Addressable

| Bit   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|

| Name  | EA  | ESPI0 | ET2 | ES0 | ET1 | EX1 | ET0 | EX0 |

| Type  | R/W | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 0   | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

0: Disable all interrupt sources. 1: Enable each interrupt according to its individual mask setting. Enable Serial Peripheral Interface (SPI0) Interrupt. This bit sets the masking of the SPI0 interrupts. 0: Disable all SPI0 interrupts. 1: Enable interrupt requests generated by SPI0. 5 ET2 Enable Timer 2 Interrupt. This bit sets the masking of the Timer 2 interrupt. 0: Disable Timer 2 interrupt. 1: Enable interrupt requests generated by the TF2L or TF2H flags. Enable UART0 Interrupt. This bit sets the masking of the UART0 interrupt. 0: Disable UART0 interrupt. 1: Enable UART0 interrupt. Enable Timer 1 Interrupt. 3 This bit sets the masking of the Timer 1 interrupt. 0: Disable all Timer 1 interrupt. 1: Enable interrupt requests generated by the TF1 flag. EX1 Enable External Interrupt 1. This bit sets the masking of External Interrupt 1. 0: Disable external interrupt 1.

> Quadro 2 – Registrador IE Fonte: (Silicon Labs, 2011)

1: Enable interrupt requests generated by the INT1 input.

1: Enable interrupt requests generated by the TF0 flag.

1: Enable interrupt requests generated by the INTO input.

This bit sets the masking of the Timer 0 interrupt.

This bit sets the masking of External Interrupt 0.

Enable Timer 0 Interrupt.

0: Disable all Timer 0 interrupt.

Enable External Interrupt 0.

0: Disable external interrupt 0.

ET0

EX0

0

# IP (Interrupt Priority)

O Quadro 3 descreve o registrador IP.

| Bit   | 7 | 6     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---|-------|-----|-----|-----|-----|-----|-----|

| Name  |   | PSPI0 | PT2 | PS0 | PT1 | PX1 | PT0 | PX0 |

| Type  | R | R/W   | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset | 1 | 0     | 0   | 0   | 0   | 0   | 0   | 0   |

|                                                           |        |                                                                                                  |                                                                                                                       | _ | _ | -        | _ | _ |  |  |  |

|-----------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---|---|----------|---|---|--|--|--|

| SFR Address = 0xB8; SFR Page = All Pages; Bit-Addressable |        |                                                                                                  |                                                                                                                       |   |   |          |   |   |  |  |  |

| Bit                                                       | Name   |                                                                                                  | Function                                                                                                              |   |   |          |   |   |  |  |  |

| 7                                                         | Unused | Read = 1b, W                                                                                     | Read = 1b, Write = Don't Care.                                                                                        |   |   |          |   |   |  |  |  |

| 6                                                         | PSPI0  | Serial Periph                                                                                    | Serial Peripheral Interface (SPI0) Interrupt Priority Control.                                                        |   |   |          |   |   |  |  |  |

|                                                           |        | This bit sets th                                                                                 |                                                                                                                       |   |   |          |   |   |  |  |  |

|                                                           |        |                                                                                                  | D: SPI0 interrupt set to low priority level.                                                                          |   |   |          |   |   |  |  |  |

|                                                           |        |                                                                                                  | 1: SPI0 interrupt set to high priority level.                                                                         |   |   |          |   |   |  |  |  |

| 5                                                         | PT2    |                                                                                                  | Timer 2 Interrupt Priority Control. This bit sets the priority of the Timer 2 interrupt.                              |   |   |          |   |   |  |  |  |

|                                                           |        |                                                                                                  |                                                                                                                       |   |   |          |   |   |  |  |  |

|                                                           |        |                                                                                                  | Timer 2 interrupt set to low priority level.     Timer 2 interrupt set to high priority level.                        |   |   |          |   |   |  |  |  |

| 4                                                         | PS0    | UART0 Interr                                                                                     | JARTO Interrupt Priority Control.                                                                                     |   |   |          |   |   |  |  |  |

|                                                           |        |                                                                                                  | This bit sets the priority of the UARTO interrupt.                                                                    |   |   |          |   |   |  |  |  |

|                                                           |        |                                                                                                  | 0: UART0 interrupt set to low priority level.                                                                         |   |   |          |   |   |  |  |  |

|                                                           |        | 1: UART0 inte                                                                                    | 1: UART0 interrupt set to high priority level.                                                                        |   |   |          |   |   |  |  |  |

| 3                                                         | PT1    |                                                                                                  | Timer 1 Interrupt Priority Control.                                                                                   |   |   |          |   |   |  |  |  |

|                                                           |        |                                                                                                  | This bit sets the priority of the Timer 1 interrupt.                                                                  |   |   |          |   |   |  |  |  |

|                                                           |        | D: Timer 1 interrupt set to low priority level. 1: Timer 1 interrupt set to high priority level. |                                                                                                                       |   |   |          |   |   |  |  |  |

| 2                                                         | PX1    |                                                                                                  |                                                                                                                       |   |   |          |   |   |  |  |  |

| -                                                         | I AI   |                                                                                                  | External Interrupt 1 Priority Control.  This bit sets the priority of the External Interrupt 1 interrupt.             |   |   |          |   |   |  |  |  |

|                                                           |        | 0: External Interrupt 1 set to low priority level.                                               |                                                                                                                       |   |   |          |   |   |  |  |  |

|                                                           |        | 1: External Interrupt 1 set to high priority level.                                              |                                                                                                                       |   |   |          |   |   |  |  |  |

| 1                                                         | PT0    | Timer 0 Interrupt Priority Control.                                                              |                                                                                                                       |   |   |          |   |   |  |  |  |

|                                                           |        | This bit sets the priority of the Timer 0 interrupt.                                             |                                                                                                                       |   |   |          |   |   |  |  |  |

|                                                           |        | 0: Timer 0 interrupt set to low priority level. 1: Timer 0 interrupt set to high priority level. |                                                                                                                       |   |   |          |   |   |  |  |  |

|                                                           | PX0    |                                                                                                  |                                                                                                                       |   |   |          |   |   |  |  |  |

| 0                                                         | PXU    | External Inter                                                                                   | •                                                                                                                     | • |   | oterrunt |   |   |  |  |  |

|                                                           |        |                                                                                                  | This bit sets the priority of the External Interrupt 0 interrupt.  0: External Interrupt 0 set to low priority level. |   |   |          |   |   |  |  |  |

|                                                           |        | 1: External Interrupt 0 set to high priority level.                                              |                                                                                                                       |   |   |          |   |   |  |  |  |

Quadro 3 – Registrador IP Fonte: (Silicon Labs, 2011)

# Interrupções Externas (INT0 E INT1)

A INTO e INT1, fontes de interrupções externas, podem ser ativas em baixo ou alto e por borda ou nível. Os *bits* IN0PL (INT0 *polarity*) e IN1PL (INT1 *polarity*), pertencentes ao registrador IT01CFestabelecem se as interrupções serão ativas em alto ou baixo. Os *bits* IT0 e IT1, do registrador TCON, selecionam se determinada interrupção será sensível a nível ou a borda. Ver Quadro 4.

| IT0 | IN0PL | INT0 Interrupt               |  |  |  |

|-----|-------|------------------------------|--|--|--|

| 1   | 0     | Active low, edge sensitive   |  |  |  |

| 1   | 1     | Active high, edge sensitive  |  |  |  |

| 0   | 0     | Active low, level sensitive  |  |  |  |

| 0   | 1     | Active high, level sensitive |  |  |  |

6

5

IN1SL[2:0]

R/W

Bit

Name

Type

IN1PL

R/W

| IT1 | IN1PL | INT1 Interrupt               |

|-----|-------|------------------------------|

| 1   | 0     | Active low, edge sensitive   |

| 1   | 1     | Active high, edge sensitive  |

| 0   | 0     | Active low, level sensitive  |

| 0   | 1     | Active high, level sensitive |

Quadro 4 – Configuração de interrupções Fonte: (Silicon Labs 2011)

A INTO e INT1 são definidas em qual pino e *port* serão acionadas no registrador IT01CF como mostra o Quadro 5.

4

3

IN0PL

R/W

2

1

IN0SL[2:0]

R/W

0

| .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                     |                                                      |                                 |                               |                               |                             |  |

|-----------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-------------------------------|-------------------------------|-----------------------------|--|

| Rese                                    | t 0   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                   | 0                                                    | 0                               | 0                             | 0                             | 1                           |  |

| SFR Address = 0xE4; SFR Page = 0        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                     |                                                      |                                 |                               |                               |                             |  |

| Bit                                     | Name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                     |                                                      |                                 |                               |                               |                             |  |

| 7                                       | IN1PL | INT1 Polarity. 0: INT1 input is active low. 1: INT1 input is active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                     |                                                      |                                 |                               |                               |                             |  |

| 6:4                                     |       | INT1 Port Pin Selection Bits.  These bits select which Port pin is assigned to INT1. Note that this pin assignment is independent of the Crossbar; INT1 will monitor the assigned Port pin without disturbing the peripheral that has been assigned the Port pin via the Crossbar. The Crossbar will not assign the Port pin to a peripheral if it is configured to skip the selected pin. 000: Select P0.0 001: Select P0.1 010: Select P0.2 011: Select P0.3 100: Select P0.4 101: Select P0.5 110: Select P0.5 111: Select P0.6 111: Select P0.7 |                                                                                     |                                                      |                                 |                               |                               |                             |  |

| 3                                       | IN0PL | INTO Polarity<br>0: INTO input<br>1: INTO input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | is active low                                                                       |                                                      |                                 |                               |                               |                             |  |

| 2:0                                     |       | INTO Port Pi These bits se independent ing the periph will not assig 000: Select F 001: Select F 010: Select F 011: Select F 100: Select F 101: Select F 111: Select F 111: Select F                                                                                                                                                                                                                                                                                                                                                                | elect which P of the Cross neral that has n the Port pi 0.0 0.1 0.2 0.3 0.4 0.5 0.6 | ort p <u>in is as</u><br>bar; INT0 w<br>s been assig | ill monitor the<br>ned the Port | e assigned F<br>pin via the ( | ort pin witho<br>Crossbar, Th | out disturb-<br>le Crossbar |  |

Quadro 5- Registrador IT01CF Fonte: (Silicon Labs, 2011)

#### 3.1.1.4 Oscilador e *Clock*

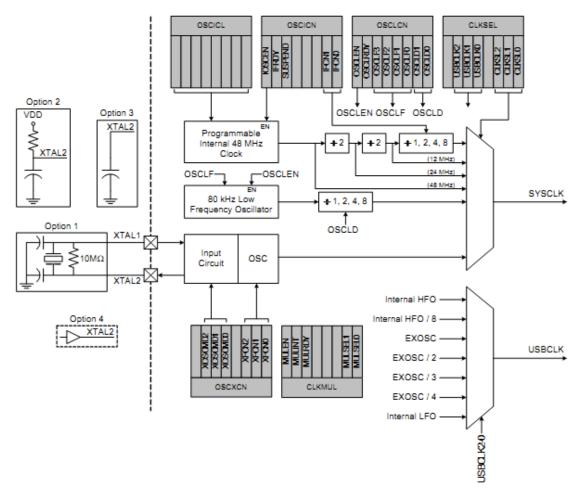

O C8051F386 possui um oscilador interno programável de alta frequência, um oscilador interno programável de baixa frequência e um circuito para oscilador externo. O oscilador interno de alta frequência pode ser ativado e ajustado nos registradores OSCICN e OSCICL como mostra a Figura 9. O oscilador interno de baixa frequência pode ser ativado e ajustado utilizando o registrador OSCLCN. O clock da interface USB (USBCLK) também pode ser derivado dos osciladores internos ou externo.

Figura 9- Opções de osciladores Fonte: (Silicon Labs, 2011)

A fonte de oscilação é definida programando o registrador CLKSEL.

## CLKSEL.

# O Quadro 6 decreve o registrador CLKSEL.

| Bit   | 7 | 6           | 5 | 4   | 3      | 2          | 1 | 0 |

|-------|---|-------------|---|-----|--------|------------|---|---|

| Name  |   | USBCLK[2:0] |   |     | OUTCLK | CLKSL[2:0] |   |   |

| Type  | R | R/W         |   | R/W | R/W    |            |   |   |

| Reset | 0 | 0           | 0 | 0   | 0      | 0          | 0 | 0 |

SFR Address = 0xA9; SFR Page = All Pages

| Bit | Name        | Function                                                                                                         |  |  |  |

|-----|-------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | Unused      | Read = 0b; Write = don't care                                                                                    |  |  |  |

| 6:4 | USBCLK[2:0] | USB Clock Source Select Bits.                                                                                    |  |  |  |

|     |             | 000: USBCLK derived from the Internal High-Frequency Oscillator.                                                 |  |  |  |

|     |             | 001: USBCLK derived from the Internal High-Frequency Oscillator / 8.                                             |  |  |  |

|     |             | 010: USBCLK derived from the External Oscillator.                                                                |  |  |  |

|     |             | 011: USBCLK derived from the External Oscillator/2.                                                              |  |  |  |

|     |             | 100: USBCLK derived from the External Oscillator/3.                                                              |  |  |  |

|     |             | 101: USBCLK derived from the External Oscillator/4.                                                              |  |  |  |

|     |             | 110: USBCLK derived from the Internal Low-Frequency Oscillator. 111: Reserved.                                   |  |  |  |

|     |             |                                                                                                                  |  |  |  |

| 3   | OUTCLK      | Crossbar Clock Out Select.                                                                                       |  |  |  |

|     |             | If the SYSCLK signal is enabled on the Crossbar, this bit selects between outputting                             |  |  |  |

|     |             | SYSCLK and SYSCLK synchronized with the Port I/O pins.                                                           |  |  |  |

|     |             | 0: Enabling the Crossbar SYSCLK signal outputs SYSCLK.                                                           |  |  |  |

|     |             | Enabling the Crossbar SYSCLK signal outputs SYSCLK synchronized with the Port I/O.                               |  |  |  |

| 2:0 | CLKSL[2:0]  | System Clock Source Select Bits.                                                                                 |  |  |  |

|     |             | 000: SYSCLK derived from the Internal High-Frequency Oscillator and scaled per the IFCN bits in register OSCICN. |  |  |  |

|     |             | 001: SYSCLK derived from the External Oscillator circuit.                                                        |  |  |  |

|     |             | 010: SYSCLK derived from the Internal High-Frequency Oscillator / 2.                                             |  |  |  |

|     |             | 011: SYSCLK derived from the Internal High-Frequency Oscillator.                                                 |  |  |  |

|     |             | 100: SYSCLK derived from the Internal Low-Frequency Oscillator and scaled per                                    |  |  |  |

|     |             | the OSCLD bits in register OSCLCN.                                                                               |  |  |  |

|     |             | 101-111: Reserved.                                                                                               |  |  |  |

Quadro 6 – Registrado CLKSEL Fonte: (Silicon Labs, 2011)

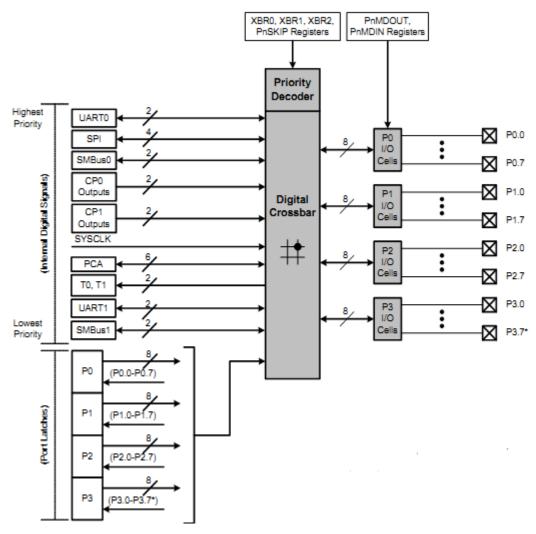

## 3.1.1.5 Entradas e saídas

O C8051F386 possui 40 pinos de entradas e saídas que estão distribuídos conforme a Figura 10. Cada pino pode ser definido como de uso geral ou entrada analógica. Essa flexibilidade proporciona ao programador ter total controle sobre todos os pinos do microcontrolador, ficando seus projetos limitados somente ao número de pinos disponíveis. Essa flexibilidade de programação de recursos é obtida através de um decodificador denominado *Digital Crossbar*.

Figura 10 - Diagrama de blocos dos pinos de entrada e saída Fonte: (Silicon Labs)

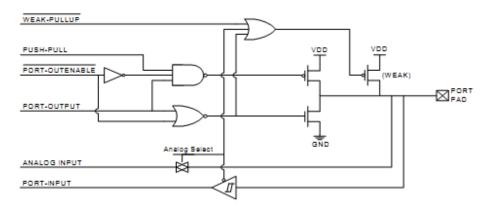

A Figura 11 mostra o diagrama esquemático das possíveis configurações de um pino de entrada e saída.

Figura 11 - Esquemático de um pino Fonte: (Silicon Labs)

#### 3.1.1.6 Timer

O C8051F386 possui 6contadores (*timers/counters*). Dois de 16 *bits* de uso geral e 4 de recarga automática para uso com a SMBus ou para uso geral com configuração e modos de funcionamento iguais ao 8051 da Intel. Estes *timers* podem ser utilizados para contagem de tempo, interrupções ou contagem de eventos externos.

| Timer 0 and Timer 1 Modes:              | Timer 2, 3, 4, and 5 Modes:       |  |

|-----------------------------------------|-----------------------------------|--|

| 13-bit counter/timer                    | 16-bit timer with auto-reload     |  |

| 16-bit counter/timer                    |                                   |  |

| 8-bit counter/timer with auto-reload    | Two 8-bit timers with auto-reload |  |

| Two 8-bit counter/timers (Timer 0 only) |                                   |  |

Quadro 7- Distribuição dos Timers Fonte: (Silicon Labs)

O *clock* para os *timers* são definidos nos registradores CKCON e CKCON1. Os *timers* são controlados programando o registrador TCON e definidos seus modos de operação no TMOD.

# 3.1.2. C8051F321

O microcontrolador C8051F321 é um controlador de 16 *bit*s da família C8051F32x desenvolvido pela *Silicon Labs*. Sua arquitetura (registradores, interrupções e *timer*) é semelhante a do C8051F31, com algumas diferenças pontuais que serão listadas abaixo.

- Oscilador interno de 25 MHz;

- Memória FLASH de 16 kbytes;

- Uma interface SMBus/I2C;

- Uma interface UART;

- Quatro timers (16 bits);

- Dois ports de Entrada/Saída (21 pinos Tensão máxima 5V);

- Sensor de temperatura;

Conversor Digital Analógico de 10 bits.

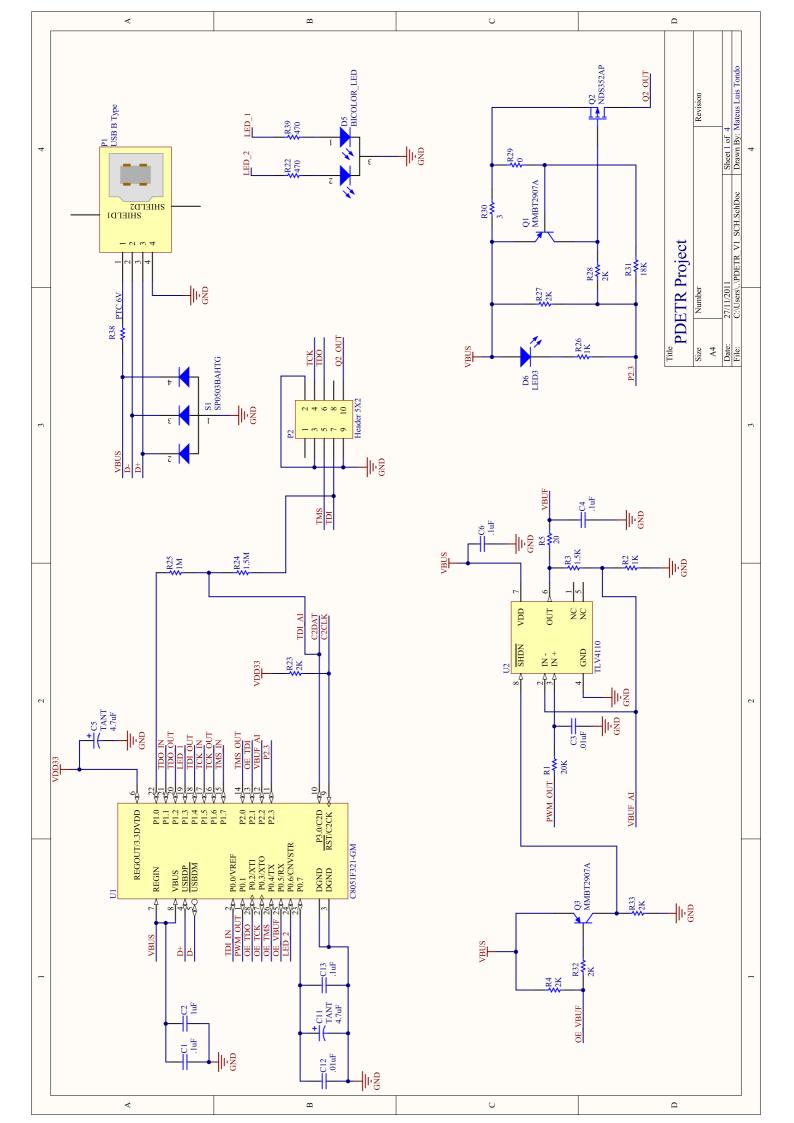

### 3.2. PROTOCOLO SILICON LABS C2

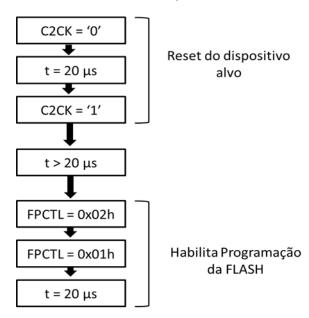

O protocolo *Silicon Labs* 2-wire, ou C2, é um protocolo de comunicação serial a dois fios desenvolvido de maneira a permitir a programação em seu próprio sistema (*in-system*), depuração (*debugging*) e varredura periférica (*boundary scan*) utilizando-se de baixo número de conexões físicas para dispositivos *Silicon Labs*. Esse modelo de comunicação envolve um dispositivo mestre (*master*), responsável pelas atividades de programação, teste e depuração em um dispositivo alvo, ou escravo, cuja interface será submetida a tais ações.

Os dois pinos físicos envolvidos são o de dados (C2D) e o *clock* (C2CK), entretanto a característica mais interessante é que o protocolo facilita o esquema de compartilhamento de pinos, visto que tais ligações não são exclusivas à interface C2 (C2I), ao contrário dos pinos JTAG. Quando o dispositivo não está em uma comunicação com o mestre, ou seja, quando está ocioso, ambos os pinos ficam disponíveis para utilização do usuário na aplicação desenvolvida.

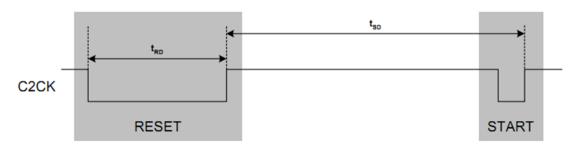

Todos os ciclos de comunicação são iniciados com um comando *START* no pino C2CK, o que permite que sejam enviados dados para a interface através de C2D e a configuração do uso da interface seja iniciada, e encerrados por um comando STOP, também em C2CK. No caso, C2CK é compartilhado com a funcionalidade de *reset* em nível baixo (/RST). Cabe ressaltar que para a inicialização da interface C2 o pino C2D deve ser alocado antes do comando *START* para tal comunicação e o mesmo deixa, desta forma, de desempenhar as funções para a qual havia sido configurado pelo usuário. Ao final da comunicação o dispositivo mestre disponibiliza novamente o pino C2D, permitindo que o mesmo volte a trabalhar como outrora configurado pelo usuário.

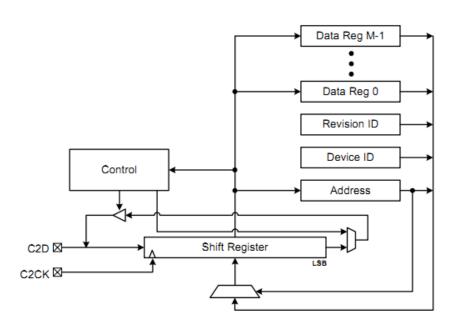

A interface C2 é similar à interface JTAG, porém, com os três sinais de dados (TDI, TDO e TMS) mapeados no pino bidirecional C2D. O sentido do fluxo, no caso de C2D, é determinado pelas instruções definidas no escopo do protocolo de forma que nunca haja conflitos entre dispositivo mestre e escravos.

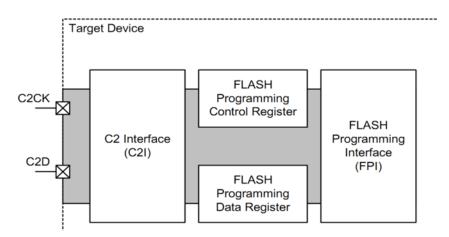

Ainda, esta interface de dois fios foi concebida para que o acesso às funcionalidades de programação e depuração sejam feitas apenas por um registrador de endereço e um grupo de registradores de dados, como mostrado pelo diagrama de blocos da interface C2 na Figura 12. O valor do registrador de

endereço, no caso, define qual registrador de dados será acessado nos ciclos de escrita e leitura, de maneira similar ao registrador de instruções JTAG, o que é possível por meio de um único *shift-register* que trabalha como um conversor paralelo-serial-paralelo comum para a interface.

Figura 12- Diagrama de blocos da interface C2 (C2I) Fonte: (Silicon Labs, 2011).

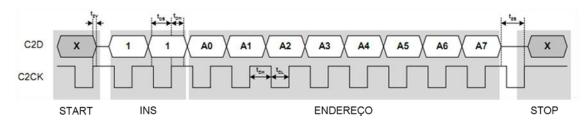

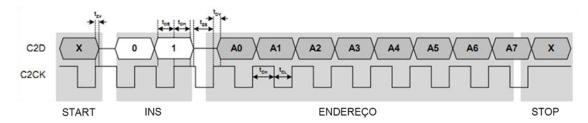

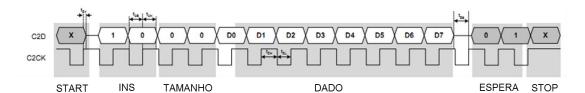

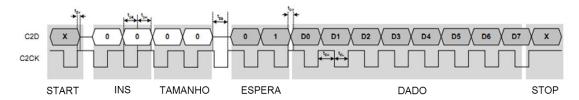

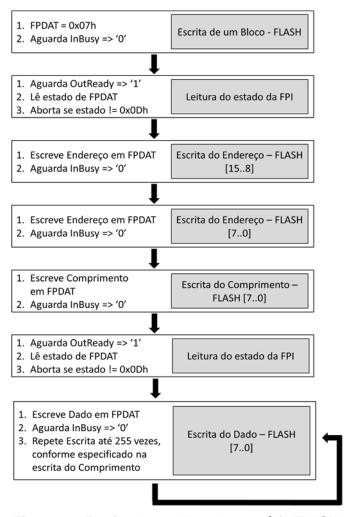

## 3.2.1. Modelo de instruções